## CHAPTER

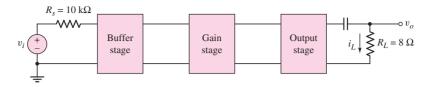

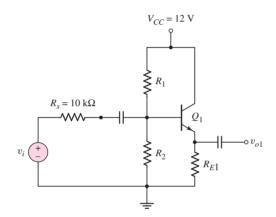

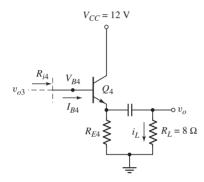

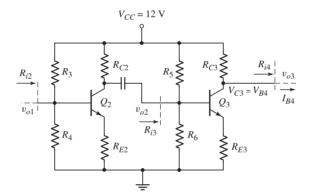

# **Basic BJT Amplifiers**

In the previous chapter, we described the structure and operation of the bipolar junction transistor, and analyzed and designed the dc response of circuits containing these devices. In this chapter, we emphasize the use of the bipolar transistor in linear amplifier applications. Linear amplifiers imply that, for the most part, we are dealing with analog signals. The magnitude of an analog signal may have any value, within limits, and may vary continuously with respect to time. A linear amplifier then means that the output signal is equal to the input signal multiplied by a constant, where the magnitude of the constant of proportionality is, in general, greater than unity.

Courtesy of Mesa Boogie, Inc.

## **PREVIEW**

In this chapter, we will:

- Understand the concept of an analog signal and the principle of a linear amplifier.

- Investigate the process by which a transistor circuit can amplify a small, time-varying input signal.

- Discuss the three basic transistor amplifier configurations.

- Analyze the common-emitter amplifier.

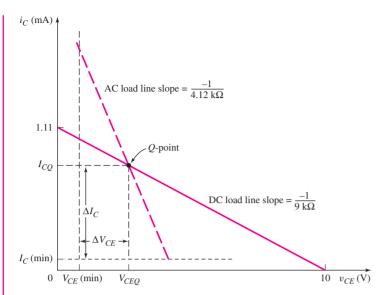

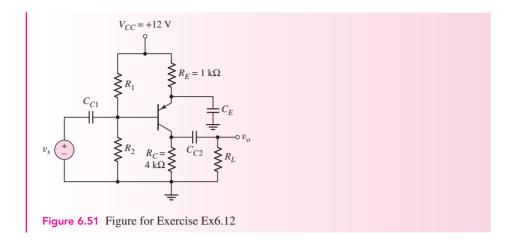

- Understand the concept of the ac load line and determine the maximum symmetrical swing of the output signal.

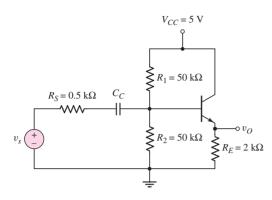

- Analyze the emitter-follower amplifier.

- Analyze the common-base amplifier.

- Compare the general characteristics of the three basic amplifier configurations.

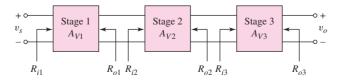

- Analyze multitransistor or multistage amplifiers.

- Understand the concept of signal power gain in an amplifier circuit.

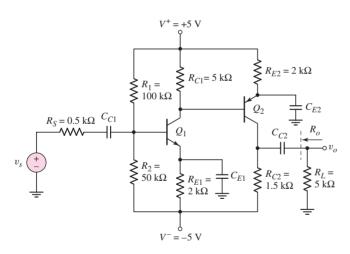

- Incorporate the bipolar transistor in a design application of a multistage transistor amplifier circuit configuration to provide a specified output signal power.

### 6.1 ANALOG SIGNALS AND LINEAR AMPLIFIERS

**Objective:** • Understand the concept of an analog signal and the principle of a linear amplifier.

In this chapter, we will be considering **signals, analog** circuits, and **amplifiers.** A signal contains some type of information. For example, sound waves produced by a speaking human contain the information the person is conveying to another person. Our physical senses, such as hearing, vision, and touch, are naturally analog. Analog signals can represent parameters such as temperature, pressure, and wind velocity. Here, we are interested in electrical signals, such as the output signal from a compact disc, a signal from a microphone, or a signal from a heart rate monitor. The electrical signals are in the form of time-varying currents and voltages.

The magnitude of an **analog signal** can take on any value within limits and may vary continuously with time. Electronic circuits that process analog signals are called **analog circuits.** One example of an analog circuit is a linear amplifier. A **linear amplifier** magnifies an input signal and produces an output signal whose magnitude is larger and directly proportional to the input signal.

In many modern day systems, signals are processed, transmitted, or received in digital form. In order to produce an analog signal, these digital signals need to be processed through a digital-to-analog (D/A) converter. D/A and A/D (analog-todigital) converters are considered in Chapter 16. In this chapter, we will assume that we already have an analog signal that needs to be amplified.

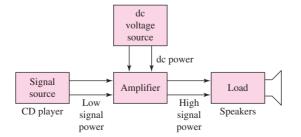

Time-varying signals from a particular source very often need to be amplified before the signal is capable of being "useful." For example, Figure 6.1 shows a signal source that is the output of a compact disc system. We assume the signal source is the output of the D/A converter and this signal consists of a small time-varying voltage and current, which means the signal power is relatively small. The power required to drive the speakers is larger than the output signal from the compact disc, so the compact disc signal must be amplified before it is capable of driving the speakers in order that sound can be heard. Other examples of signals that must be amplified before they are capable of driving loads include the output of a microphone, voice signals received on earth from an orbiting manned shuttle, video signals from an orbiting weather satellite, and the output of an EKG.

Also shown in Figure 6.1 is a dc voltage source connected to the amplifier. The amplifier contains transistors that must be biased in the forward-active region so that the transistors can act as amplifying devices. We want the output signal to be linearly proportional to the input signal so that the output of the speakers is an exact (as much

Figure 6.1 Block diagram of a compact disc player system

as possible) reproduction of the signal generated from the compact disc. Therefore, we want the amplifier to be a **linear** amplifier.

Figure 6.1 suggests that there are two types of analyses of the amplifier that we must consider. The first is a dc analysis because of the applied dc voltage source, and the second is a time-varying or ac analysis because of the time-varying signal source. A linear amplifier means that the superposition principle applies. The principle of superposition states: *The response of a linear circuit excited by multiple independent input signals is the sum of the responses of the circuit to each of the input signals alone.*

For the linear amplifier, then, the dc analysis can be performed with the ac source set to zero. This analysis, called a *large signal analysis*, establishes the *Q*-point of the transistors in the amplifier. This analysis and design was the primary objective of the previous chapter. The ac analysis, called a *small-signal analysis*, can be performed with the dc source set to zero. The total response of the amplifier circuit is the sum of the two individual responses.

## 6.2 THE BIPOLAR LINEAR AMPLIFIER

**Objective:** Investigate the process by which a single-transistor circuit can amplify a small, time-varying input signal and develop the small-signal models of the transistor that are used in the analysis of linear amplifiers.

The transistor is the heart of an amplifier. In this chapter, we will consider bipolar transistor amplifiers. Bipolar transistors have traditionally been used in linear amplifier circuits because of their relatively high gain.

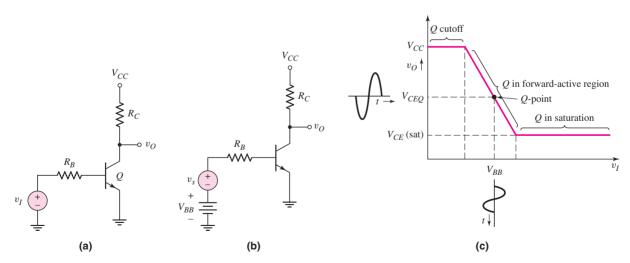

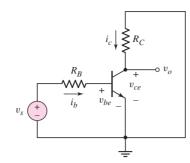

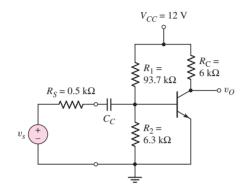

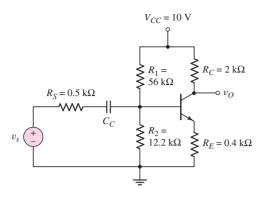

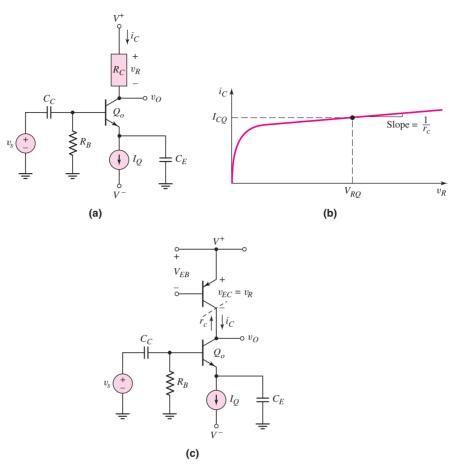

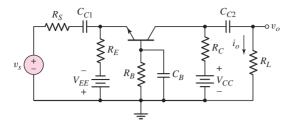

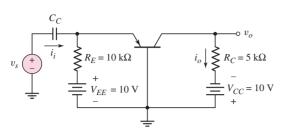

We begin our discussion by considering the same bipolar circuit that was discussed in the last chapter. Figure 6.2(a) shows the circuit where the input signal  $v_I$

Figure 6.2 (a) Bipolar transistor inverter circuit, (b) inverter circuit showing both dc bias and ac signal sources in the base circuit, and (c) transistor inverter voltage transfer characteristics showing desired Q-point

contains both a dc and an ac signal. Figure 6.2(b) shows the same circuit where  $V_{BB}$  is a dc voltage to bias the transistor at a particular *Q*-point and  $v_s$  is the ac signal that is to be amplified. Figure 6.2(c) shows the voltage transfer characteristics that were developed in Chapter 5. To use the circuit as an amplifier, the transistor needs to be biased with a dc voltage at a quiescent point (*Q*-point), as shown in the figure, such that the transistor is biased in the forward-active region. This dc analysis or design of the circuit was the focus of our attention in Chapter 5. If a time-varying (e.g., sinusoidal) signal is superimposed on the dc input voltage,  $V_{BB}$ , the output voltage will change along the transfer curve producing a time-varying output voltage. If the time-varying output voltage is directly proportional to and larger than the time-varying input voltage, then the circuit is a linear amplifier. From this figure, we see that if the transistor is not biased in the active region (biased either in cutoff or saturation), the output voltage does not change with a change in the input voltage. Thus, we no longer have an amplifier.

In this chapter, we are interested in the ac analysis and design of bipolar transistor amplifiers, which means that we must determine the relationships between the time-varying output and input signals. We will initially consider a graphical technique that can provide an intuitive insight into the basic operation of the circuit. We will then develop a small-signal equivalent circuit that will be used in the mathematical analysis of the ac signals. In general, we will be considering a steady-state, sinusoidal analysis of circuits. We will assume that any time-varying signal can be written as a sum of sinusoidal signals of different frequencies and amplitudes (Fourier series), so that a sinusoidal analysis is appropriate.

We will be dealing with time-varying as well as dc currents and voltages in this chapter. Table 6.1 gives a summary of notation that will be used. This notation was discussed in the Prologue, but is repeated here for convenience. A lowercase letter with an uppercase subscript, such as  $i_B$  or  $v_{BE}$ , indicates *total instantaneous values*.

| Table 6.1     | Summary of notation        |  |

|---------------|----------------------------|--|

| Variable      | Meaning                    |  |

| $i_B, v_{BE}$ | Total instantaneous values |  |

| $I_B, V_{BE}$ | DC values                  |  |

| $i_b, v_{be}$ | Instantaneous ac values    |  |

| $I_b, V_{be}$ | Phasor values              |  |

An uppercase letter with an uppercase subscript, such as  $I_B$  or  $V_{BE}$ , indicates dc quantities. A lowercase letter with a lowercase subscript, such as  $i_b$  or  $v_{be}$ , indicates instantaneous values of *ac signals*. Finally, an upper-case letter with a lowercase subscript, such as  $I_b$  or  $V_{be}$ , indicates *phasor quantities*. The phasor notation, which was reviewed in the Prologue becomes especially important in Chapter 7 during the discussion of frequency response. However, the phasor notation will be generally used in this chapter in order to be consistent with the overall ac analysis.

#### 6.2.1 Graphical Analysis and ac Equivalent Circuit

Figure 6.3 shows the same basic bipolar inverter circuit that has been discussed, but now includes a sinusoidal signal source in series with the dc source as was shown in Figure 6.2(b).

Figure 6.3 A common-emitter circuit with a time-varying signal source in series with the base dc source

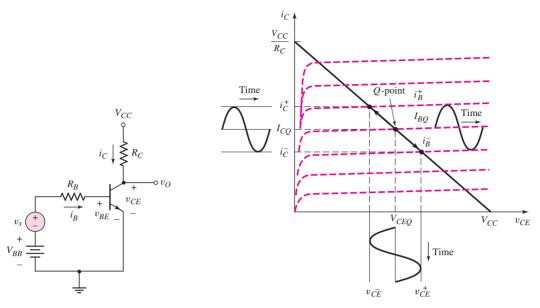

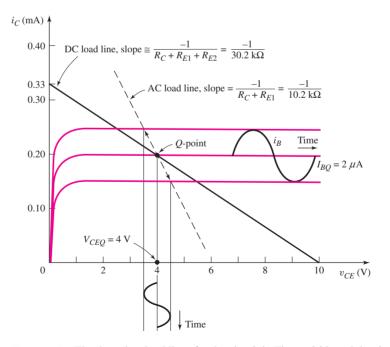

**Figure 6.4** Common-emitter transistor characteristics, dc load line, and sinusoidal variation in base current, collector current, and collector–emitter voltage

Figure 6.4 shows the transistor characteristics, the dc load line, and the *Q*-point. The sinusoidal signal source,  $v_s$ , will produce a time-varying or ac base current superimposed on the quiescent base current as shown in the figure. The time-varying base current will induce an ac collector current superimposed on the quiescent collector current. The ac collector current then produces a time-varying voltage across  $R_c$ , which induces an ac collector–emitter voltage as shown in the figure. The ac collector–emitter voltage, in general, will be larger than the sinusoidal input signal, so that the circuit has produced signal amplification—that is, the circuit is an amplifier.

We need to develop a mathematical method or model for determining the relationships between the sinusoidal variations in currents and voltages in the circuit. As already mentioned, a linear amplifier implies that superposition applies so that the dc and ac analyses can be performed separately. To obtain a linear amplifier, the time-varying or ac currents and voltages must be small enough to ensure a linear relation between the ac signals. To meet this objective, the time-varying signals are assumed to be *small signals*, which means that the amplitudes of the ac signals are small enough to yield linear relations. The concept of "small enough," or small signal, will be discussed further as we develop the small-signal equivalent circuits.

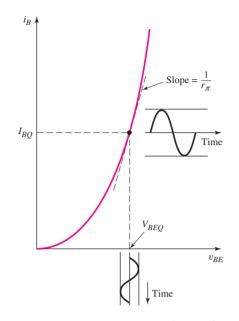

A time-varying signal source,  $v_s$ , in the base of the circuit in Figure 6.3 generates a time-varying component of base current, which implies there is also a timevarying component of base–emitter voltage. Figure 6.5 shows the exponential relationship between base-current and base–emitter voltage. If the magnitudes of the time-varying signals that are superimposed on the dc quiescent point are small, then we can develop a linear relationship between the ac base–emitter voltage and ac base current. This relationship corresponds to the slope of the curve at the Q-point.

**Figure 6.5** Base current versus base-emitter voltage characteristic with superimposed sinusoidal signals. Slope at the *Q*-point is inversely proportional to  $r_{\pi}$ , a small-signal parameter.

Using Figure 6.5, we can now determine one quantitative definition of small signal. From the discussion in Chapter 5, in particular, Equation (5.6), the relation between base–emitter voltage and base current can be written as

$$i_B = \frac{I_S}{\beta} \cdot \exp\left(\frac{v_{BE}}{V_T}\right) \tag{6.1}$$

If  $v_{BE}$  is composed of a dc term with a sinusoidal component superimposed, i.e.,  $v_{BE} = V_{BEQ} + v_{be}$ , then

$$i_B = \frac{I_S}{\beta} \cdot \exp\left(\frac{V_{BEQ} + v_{be}}{V_T}\right) = \frac{I_S}{\beta} \cdot \exp\left(\frac{V_{BEQ}}{V_T}\right) \cdot \exp\left(\frac{v_{be}}{V_T}\right)$$

(6.2)

where  $V_{BEQ}$  is normally referred to as the base–emitter turn-on voltage,  $V_{BE}$ (on). The term  $[I_S/\beta] \cdot \exp(V_{BEQ}/V_T)$  is the quiescent base current, so we can write

$$i_B = I_{BQ} \cdot \exp\left(\frac{v_{be}}{V_T}\right) \tag{6.3}$$

The base current, given in this form, is not linear and cannot be written as an ac current superimposed on a dc quiescent value. However, if  $v_{be} \ll V_T$ , then we can expand the exponential term in a Taylor series, keeping only the **linear term**. This approximation is what is meant by **small signal**. We then have

$$i_B \cong I_{BQ} \left( 1 + \frac{v_{be}}{V_T} \right) = I_{BQ} + \frac{I_{BQ}}{V_T} \cdot v_{be} = I_{BQ} + i_b$$

(6.4(a))

where  $i_b$  is the time-varying (sinusoidal) base current given by

$$i_b = \left(\frac{I_{BQ}}{V_T}\right) v_{be} \tag{6.4(b)}$$

The sinusoidal base current,  $i_b$ , is linearly related to the sinusoidal base–emitter voltage,  $v_{be}$ . In this case, the term small-signal refers to the condition in which  $v_{be}$  is sufficiently small for the linear relationships between  $i_b$  and  $v_{be}$  given by Equation (6.4(b)) to be valid. As a general rule, if  $v_{be}$  is less than 10 mV, then the exponential relation given by Equation (6.3) and its linear expansion in Equation (6.4(a)) agree within approximately 10 percent. Ensuring that  $v_{be} < 10$  mV is another useful rule of thumb in the design of linear bipolar transistor amplifiers.

If the  $v_{be}$  signal is assumed to be sinusoidal, but if its magnitude becomes too large, then the output signal will no longer be a pure sinusoidal voltage but will become distorted and contain harmonics (see box "Harmonic Distortion").

#### Harmonic Distortion

If an input sinusoidal signal becomes too large, the output signal may no longer be a pure sinusoidal signal because of nonlinear effects. A nonsinusoidal output signal may be expanded into a Fourier series and written in the form

$$v_{O}(t) = V_{O} + V_{1} \sin(\omega t + \phi_{1}) + V_{2} \sin(2\omega t + \phi_{2}) + V_{3} \sin(3\omega t + \phi_{3}) + \cdots$$

dc desired 2nd harmonic 3rd harmonic

linear output distortion distortion

(6.5)

The signal at the frequency  $\omega$  is the desired linear output signal for a sinusoidal input signal at the same frequency.

The time-varying input base-emitter voltage is contained in the exponential term given in Equation (6.3). Expanding the exponential function into a Taylor series, we find

$$e^x = 1 + x + \frac{x^2}{2} + \frac{x^3}{6} + \cdots$$

(6.6)

where, from Equation (6.3), we have  $x = v_{be}/V_T$ . If we assume the input signal is a sinusoidal function, then we can write

$$x = \frac{v_{be}}{V_T} = \frac{V_\pi}{V_T} \sin \omega t \tag{6.7}$$

The exponential function can then be written as

$$e^{x} = 1 + \frac{V_{\pi}}{V_{T}}\sin\omega t + \frac{1}{2}\cdot\left(\frac{V_{\pi}}{V_{T}}\right)^{2}\sin^{2}\omega t + \frac{1}{6}\cdot\left(\frac{V_{\pi}}{V_{T}}\right)^{3}\sin^{3}\omega t + \cdots$$

(6.8)

From trigonometric identities, we can write

$$\sin^2 \omega t = \frac{1}{2} [1 - \cos(2\omega t)] = \frac{1}{2} [1 - \sin(2\omega t + 90^\circ)]$$

(6.9a)

and

$$\sin^3 \omega t = \frac{1}{4} [3\sin\omega t - \sin(3\omega t)]$$

(6.9b)

Substituting Equations (6.9a) and (6.9b) into Equation (6.8), we obtain

$$e^{x} = \left[1 + \frac{1}{4} \left(\frac{V_{\pi}}{V_{T}}\right)^{2}\right] + \frac{V_{\pi}}{V_{T}} \left[1 + \frac{1}{8} \left(\frac{V_{\pi}}{V_{T}}\right)^{2}\right] \sin \omega t$$

$$-\frac{1}{4} \left(\frac{V_{\pi}}{V_{T}}\right)^{2} \sin(2\omega t + 90^{\circ}) - \frac{1}{24} \left(\frac{V_{\pi}}{V_{T}}\right)^{3} \sin(3\omega t) + \cdots$$

(6.10)

Comparing Equation (6.10) to Equation (6.8), we find the coefficients as

$$V_{O} = \left[1 + \frac{1}{4} \left(\frac{V_{\pi}}{V_{T}}\right)^{2}\right] \quad V_{1} = \frac{V_{\pi}}{V_{T}} \left[1 + \frac{1}{8} \left(\frac{V_{\pi}}{V_{T}}\right)^{2}\right]$$

$$V_{2} = -\frac{1}{4} \left(\frac{V_{\pi}}{V_{T}}\right)^{2} \qquad V_{3} = -\frac{1}{24} \left(\frac{V_{\pi}}{V_{T}}\right)^{3}$$

(6.11)

We see that as  $(V_{\pi}/V_T)$  increases, the second and third harmonic terms become non-zero. In addition, the dc and first harmonic coefficients also become nonlinear. A figure of merit is called the percent total harmonic distortion (THD) and is defined as

THD(%) =

$$\frac{\sqrt{\sum_{2}^{\infty} V_{n}^{2}}}{V_{1}} \times 100\%$$

(6.12)

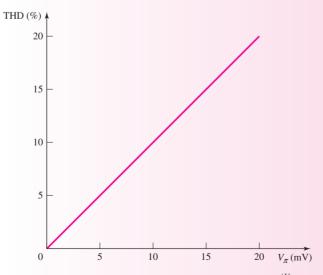

Considering only the second and third harmonic terms, the THD is plotted in Figure 6.6. We see that, for  $V_{\pi} \leq 10$  mV, the THD is less than 10 percent. This total harmonic distortion value may seem excessive, but as we will see later in Chapter 12, distortion can be reduced when feedback circuits are used.

**Figure 6.6** Total harmonic distortion of the function  $e^{v_{BE}/V_T}$ , where  $v_{BE} = V_{\pi} \sin \omega t$ , as a function of  $V_{\pi}$

From the concept of small signal, all the time-varying signals shown in Figure 6.4 will be linearly related and are superimposed on dc values. We can write (refer to notation given in Table 6.1)

$$i_B = I_{BQ} + i_b \tag{6.13(a)}$$

$$i_C = I_{CQ} + i_c \tag{6.13(b)}$$

$$v_{CE} = V_{CEQ} + v_{ce} \tag{6.13(c)}$$

and

$$v_{BE} = V_{BEQ} + v_{be} \tag{6.13(d)}$$

If the signal source,  $v_s$ , is zero, then the base–emitter and collector–emitter loop equations are

$$V_{BB} = I_{BQ}R_B + V_{BEQ} \tag{6.14(a)}$$

and

$$V_{CC} = I_{CQ}R_C + V_{CEQ} \tag{6.14(b)}$$

Taking into account the time-varying signals, we find the base-emitter loop equation is

$$V_{BB} + v_s = i_B R_B + v_{BE}$$

(6.15(a))

or

$$V_{BB} + v_s = (I_{BQ} + i_b)R_B + (V_{BEQ} + v_{be})$$

(6.15(b))

Rearranging terms, we find

$$V_{BB} - I_{BQ}R_B - V_{BEQ} = i_b R_B + v_{be} - v_s$$

(6.15(c))

From Equation (6.14(a)), the left side of Equation (6.15(c)) is zero. Equation (6.15 (c)) can then be written as

$$v_s = i_b R_B + v_{be} \tag{6.16}$$

which is the base-emitter loop equation with all dc terms set equal to zero.

Taking into account the time-varying signals, the collector-emitter loop equation is

$$V_{CC} = i_C R_C + v_{CE} = (I_{CO} + i_c) R_C + (V_{CEO} + v_{ce})$$

(6.17(a))

Rearranging terms, we find

$$V_{CC} - I_{CQ}R_C - V_{CEQ} = i_c R_C + v_{ce}$$

(6.17(b))

From Equation (6.14(b)), the left side of Equation (6.17(b)) is zero. Equation (6.17(b)) can be written as

$i_c R_C + v_{ce} = 0 (6.18)$

which is the collector-emitter loop equation with all dc terms set equal to zero.

Equations (6.16) and (6.18) relate the ac parameters in the circuit. These equations can be obtained directly by setting all dc currents and voltages equal to zero, so the dc voltage sources become short circuits and any dc current sources would become open circuits. *These results are a direct consequence of applying superposition to a linear circuit.* The resulting BJT circuit, shown in Figure 6.7, is called the *ac*

**Figure 6.7** The ac equivalent circuit of the common-emitter circuit shown in Figure 6.3. The dc voltage sources have been set equal to zero.

*equivalent circuit*, and all currents and voltages shown are time-varying signals. We should stress that this circuit is an equivalent circuit. We are implicitly assuming that the transistor is still biased in the forward-active region with the appropriate dc voltages and currents.

Another way of looking at the ac equivalent circuit is as follows. In the circuit in Figure 6.3, the base and collector currents are composed of ac signals superimposed on dc values. These currents flow through the  $V_{BB}$  and  $V_{CC}$  voltage sources, respectively. Since the voltages across these sources are assumed to remain constant, the sinusoidal currents do not produce any sinusoidal voltages across these elements. Then, since the sinusoidal voltages are zero, the equivalent ac impedances are zero, or short circuits. In other words, the dc voltage sources are ac short circuits in an equivalent ac circuit. We say that the node connecting  $R_C$  and  $V_{CC}$  is at signal ground.

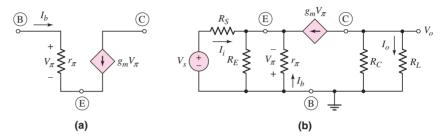

#### 6.2.2 Small-Signal Hybrid- $\pi$ Equivalent Circuit of the Bipolar Transistor

We developed the ac equivalent circuit shown in Figure 6.7. We now need to develop a **small-signal equivalent circuit** for the transistor. One such circuit is the **hybrid**- $\pi$  model, which is closely related to the physics of the transistor. This effect will become more apparent in Chapter 7 when a more detailed hybrid- $\pi$  model is developed to take into account the frequency response of the transistor.

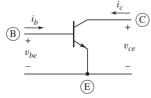

We can treat the bipolar transistor as a two-port network as shown in Figure 6.8. One element of the hybrid- $\pi$  model has already been described. Figure 6.5 showed the base current versus base–emitter voltage characteristic, with small time-varying signals superimposed at the *Q*-point. Since the sinusoidal signals are small, we can treat the slope at the *Q*-point as a constant, which has units of conductance. The inverse of this conductance is the small-signal resistance defined as  $r_{\pi}$ . We can then relate the small-signal input base current to the small-signal input voltage by

$$v_{be} = i_b r_\pi \tag{6.19}$$

where  $1/r_{\pi}$  is equal to the slope of the  $i_B-v_{BE}$  curve, as shown in Figure 6.5. From Equation (6.2), we then find  $r_{\pi}$  from

$$\frac{1}{r_{\pi}} = \frac{\partial i_B}{\partial v_{BE}} \bigg|_{Q-pt} = \frac{\partial}{\partial v_{BE}} \left[ \frac{I_S}{\beta} \cdot \exp\left(\frac{v_{BE}}{V_T}\right) \right] \bigg|_{Q-pt}$$

(6.20(a))

**Figure 6.8** The BJT as a small-signal, two-port network

or

$$\frac{1}{V_{\pi}} = \frac{1}{V_{T}} \cdot \left[ \frac{I_{S}}{\beta} \cdot \exp\left(\frac{v_{BE}}{V_{T}}\right) \right] \Big|_{Q^{-pt}} = \frac{I_{BQ}}{V_{T}}$$

(6.20(b))

Then

$$\frac{v_{be}}{i_b} = r_\pi = \frac{V_T}{I_{BQ}} = \frac{\beta V_T}{I_{CQ}}$$

(6.21)

The resistance  $r_{\pi}$  is called the **diffusion resistance** or base–emitter input resistance. We note that  $r_{\pi}$  is a function of the *Q*-point parameters.

We can consider the output terminal characteristics of the bipolar transistor. If we initially consider the case in which the output collector current is independent of the collector–emitter voltage, then the collector current is a function only of the base–emitter voltage, as discussed in Chapter 5. We can then write

$$\Delta i_C = \frac{\partial i_C}{\partial v_{BE}} \bigg|_{Q^- pt} \cdot \Delta v_{BE}$$

(6.22(a))

or

$$i_c = \frac{\partial i_C}{\partial v_{BE}} \bigg|_{Q-pt} \cdot v_{be}$$

(6.22(b))

From Chapter 5, in particular Equation (5.2), we had written

$$i_C = I_S \exp\left(\frac{v_{BE}}{V_T}\right) \tag{6.23}$$

Then

$$\frac{\partial i_C}{\partial v_{BE}}\Big|_{Q-pt} = \frac{1}{V_T} \cdot I_S \exp\left(\frac{v_{BE}}{V_T}\right)\Big|_{Q-pt} = \frac{I_{CQ}}{V_T}$$

(6.24)

The term  $I_S \exp(v_{BE}/V_T)$  evaluated at the *Q*-point is just the quiescent collector current. The term  $I_{CQ}/V_T$  is a conductance. Since this conductance relates a current in the collector to a voltage in the B–E circuit, the parameter is called a **transconductance** and is written

$$g_m = \frac{I_{CQ}}{V_T} \tag{6.25}$$

The small-signal transconductance is also a function of the *Q*-point parameters and is directly proportional to the dc bias current. The variation of transconductance with quiescent collector current will prove to be useful in amplifier design.

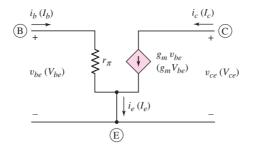

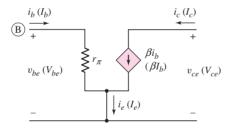

Using these new parameters, we can develop a simplified small-signal hybrid- $\pi$  equivalent circuit for the npn bipolar transistor, as shown in Figure 6.9. The phasor components are given in parentheses. This circuit can be inserted into the ac equivalent circuit previously shown in Figure 6.7.

We can develop a slightly different form for the output of the equivalent circuit. We can relate the small-signal collector current to the small-signal base current as

$$\Delta i_C = \frac{\partial i_C}{\partial i_B}\Big|_{Q^- pt} \cdot \Delta i_B \tag{6.26(a)}$$

or

$$i_c = \frac{\partial i_C}{\partial i_B}\Big|_{Q^-pt} \cdot i_b \tag{6.26(b)}$$

**Figure 6.9** A simplified small-signal hybrid- $\pi$  equivalent circuit for the npn transistor. The ac signal currents and voltages are shown. The phasor signals are shown in parentheses.

where

$$\left. \frac{\partial i_C}{\partial i_B} \right|_{Q-pt} \equiv \beta \tag{6.26(c)}$$

and is called an incremental or ac common-emitter current gain. We can then write

$$i_c = \beta i_b \tag{6.27}$$

The small-signal equivalent circuit of the bipolar transistor in Figure 6.10 uses this parameter. The parameters in this figure are also given as phasors. This circuit can also be inserted in the ac equivalent circuit given in Figure 6.7. Either equivalent circuit, Figure 6.9 or 6.10, may be used. We will use both circuits in the examples that follow in this chapter.

**Figure 6.10** BJT small-signal equivalent circuit using the common-emitter current gain. The ac signal currents and voltages are shown. The phasor signals are shown in parentheses.

#### **Common-Emitter Current Gain**

The common-emitter current gain defined in Equation (6.26(c)) is actually defined as an ac beta and does not include dc leakage currents. We discussed the commonemitter current gain in Chapter 5. We defined a dc beta as the ratio of a dc collector current to the corresponding dc base current. In this case leakage currents are included. However, we will assume in this text that leakage currents are negligible so that the two definitions of beta are equivalent.

The small-signal hybrid- $\pi$  parameters  $r_{\pi}$  and  $g_m$  were defined in Equations (6.21) and (6.25). If we multiply  $r_{\pi}$  and  $g_m$ , we find

$$r_{\pi}g_{m} = \left(\frac{\beta V_{T}}{I_{CQ}}\right) \cdot \left(\frac{I_{CQ}}{V_{T}}\right) = \beta$$

(6.28)

In general, we will assume that the common-emitter current gain  $\beta$  is a constant for a given transistor. However, we must keep in mind that  $\beta$  may vary from one device

to another and that  $\beta$  does vary with collector current. This variation with  $I_C$  will be specified on data sheets for specific discrete transistors.

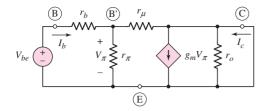

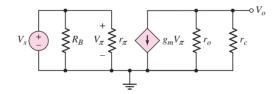

#### Small-Signal Voltage Gain

Continuing our discussion of equivalent circuits, we may now insert the bipolar, equivalent circuit in Figure 6.9, for example, into the ac equivalent circuit in Figure 6.7. The result is shown in Figure 6.11. Note that we are using the phasor notation. When incorporating the small-signal hybrid- $\pi$  model of the transistor (Figure 6.9) into the ac equivalent circuit (Figure 6.7), it is generally helpful to start with the three terminals of the transistor as shown in Figure 6.11. Then sketch the hybrid- $\pi$  equivalent circuit between these three terminals. Finally, connect the remaining circuit elements, such as  $R_B$  and  $R_C$ , to the transistor terminals. As the circuits become more complex, this technique will minimize errors in developing the small-signal equivalent circuit.

**Figure 6.11** The small-signal equivalent circuit of the common-emitter circuit shown in Figure 6.3. The small-signal hybrid- $\pi$  model of the npn bipolar transistor is shown within the dotted lines.

The **small-signal voltage gain**,  $A_v = V_o/V_s$ , of the circuit is defined as the ratio of output signal voltage to input signal voltage. We may note a new variable in Figure 6.11. The conventional phasor notation for the small-signal base-emitter voltage is  $V_{\pi}$ , called the control voltage. The dependent current source is then given by  $g_m V_{\pi}$ . The dependent current  $g_m V_{\pi}$  flows through  $R_C$ , producing a negative collector–emitter voltage, or

$$V_o = V_{ce} = -(g_m V_\pi) R_C$$

(6.29)

and, from the input portion of the circuit, we find

$$V_{\pi} = \left(\frac{r_{\pi}}{r_{\pi} + R_B}\right) \cdot V_s \tag{6.30}$$

The small-signal voltage gain is then

$$A_v = \frac{V_o}{V_s} = -(g_m R_C) \cdot \left(\frac{r_\pi}{r_\pi + R_B}\right)$$

(6.31)

#### EXAMPLE 6.1

**Objective:** Calculate the small-signal voltage gain of the bipolar transistor circuit shown in Figure 6.3.

Assume the transistor and circuit parameters are:  $\beta = 100$ ,  $V_{CC} = 12$  V,  $V_{BE} = 0.7$  V,  $R_C = 6$  k $\Omega$ ,  $R_B = 50$  k $\Omega$ , and  $V_{BB} = 1.2$  V.

**DC Solution:** We first do the dc analysis to find the *Q*-point values. We obtain

$$I_{BQ} = \frac{V_{BB} - V_{BE}(\text{on})}{R_B} = \frac{1.2 - 0.7}{50} \Rightarrow 10 \ \mu\text{A}$$

so that

$$I_{CQ} = \beta I_{BQ} = (100)(10 \ \mu \text{A}) \Rightarrow 1 \text{ mA}$$

Then,

$$V_{CEQ} = V_{CC} - I_{CQ}R_C = 12 - (1)(6) = 6 V$$

Therefore, the transistor is biased in the forward-active mode, as can be seen from Figure 5.25 in Chapter 5. In particular, for the npn transistor,  $V_{BE} > 0$  and  $V_{BC} < 0$  for the forward-active mode.

**AC Solution:** The small-signal hybrid- $\pi$  parameters are

$$r_{\pi} = \frac{\beta V_T}{I_{CO}} = \frac{(100)(0.026)}{1} = 2.6 \,\mathrm{k\Omega}$$

and

$$g_m = \frac{I_{CQ}}{V_T} = \frac{1}{0.026} = 38.5 \text{ mA/V}$$

The small-signal voltage gain is determined using the small-signal equivalent circuit shown in Figure 6.11. From Equation (6.31), we find

$$A_v = \frac{V_o}{V_s} = -(g_m R_C) \cdot \left(\frac{r_\pi}{r_\pi + R_B}\right)$$

or

$$= -(38.5)(6)\left(\frac{2.6}{2.6+50}\right) = -11.4$$

**Comment:** We see that the magnitude of the sinusoidal output voltage is 11.4 times the magnitude of the sinusoidal input voltage. We will see that other circuit configurations result in even larger small-signal voltage gains.

Discussion: We may consider a specific sinusoidal input voltage. Let

$$v_s = 0.25 \sin \omega t V$$

The sinusoidal base current is given by

$$i_b = \frac{v_s}{R_B + r_\pi} = \frac{0.25 \sin \omega t}{50 + 2.6} \to 4.75 \sin \omega t \ \mu A$$

The sinusoidal collector current is

$i_c = \beta i_b = (100)(4.75 \sin \omega t) \rightarrow 0.475 \sin \omega t \text{ mA}$

and the sinusoidal collector-emitter voltage is

$$v_{ce} = -i_c R_C = -(0.475)(6) \sin \omega t = -2.85 \sin \omega t V$$

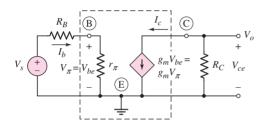

Figure 6.12 shows the various currents and voltages in the circuit. These include the sinusoidal signals superimposed on the dc values. Figure 6.12(a) shows the sinusoidal

**Figure 6.12** The dc and ac signals in the common-emitter circuit: (a) input voltage signal, (b) input base current, (c) output collector current, and (d) output collector-emitter voltage. The ac output voltage is 180° out of phase with respect to the input voltage signal.

input voltage, and Figure 6.12(b) shows the sinusoidal base current superimposed on the quiescent value. The sinusoidal collector current superimposed on the dc quiescent value is shown in Figure 6.12(c). Note that, as the base current increases, the collector current increases.

Figure 6.12(d) shows the sinusoidal component of the C–E voltage superimposed on the quiescent value. As the collector current increases, the voltage drop across  $R_C$ increases so that the C–E voltage decreases. Consequently, the sinusoidal component of the output voltage is 180 degrees out of phase with respect to the input signal voltage. The minus sign in the voltage gain expression represents this 180-degree **phase shift.** In summary, the signal was both amplified and inverted by this amplifier.

**Analysis Method:** To summarize, the analysis of a BJT amplifier proceeds as shown in the box "Problem Solving Method: Bipolar AC Analysis."

#### **EXERCISE PROBLEM**

**Ex 6.1:** The circuit parameters in Figure 6.3 are  $V_{CC} = 5$  V,  $V_{BB} = 2$  V,  $R_B = 650 \text{ k}\Omega$ , and  $R_C = 15 \text{ k}\Omega$ . The transistor parameters are  $\beta = 100$  and  $V_{BE}(\text{on}) = 0.7$  V. (a) Determine the *Q*-point values  $I_{CQ}$  and  $V_{CEQ}$ . (b) Find the small-signal hybrid- $\pi$  parameters  $g_m$  and  $r_{\pi}$ . (c) Calculate the small-signal voltage gain. (Ans. (a)  $I_{CQ} = 0.2$  mA,  $V_{CEQ} = 2$  V; (b)  $g_m = 7.69 \text{ mA/V}$ ,  $r_{\pi} = 13 \text{ k}\Omega$ ; (c)  $A_v = -2.26$ )

#### Problem-Solving Technique: Bipolar AC Analysis

Since we are dealing with linear amplifier circuits, superposition applies, which means that we can perform the dc and ac analyses separately. The analysis of the BJT amplifier proceeds as follows:

1. Analyze the circuit with only the dc sources present. This solution is the dc or quiescent solution, which uses the dc signal models for the elements, as listed

in Table 6.2. The transistor must be biased in the forward-active region in order to produce a linear amplifier.

- 2. Replace each element in the circuit with its small-signal model, as shown in Table 6.2. The small-signal hybrid- $\pi$  model applies to the transistor although it is not specifically listed in the table.

- 3. Analyze the small-signal equivalent circuit, setting the dc source components equal to zero, to produce the response of the circuit to the time-varying input signals only.

| Table 6.2                  | Transformation of elements in dc and small-signal analysis |                   |                   |

|----------------------------|------------------------------------------------------------|-------------------|-------------------|

| Element                    | <i>I–V</i> relationship                                    | DC model          | AC model          |

| Resistor                   | $I_R = \frac{V}{R}$                                        | R                 | R                 |

| Capacitor                  | $I_C = sCV$                                                | Open              | С                 |

|                            |                                                            | o o               |                   |

| Inductor                   | $I_L = \frac{V}{sL}$                                       | Short<br>—∞—∞—    | L                 |

| Diode                      | $I_D = I_S(e^{v_D/V_T} - 1)$                               | $+V_{\gamma}-r_f$ | $r_d = V_T / I_D$ |

| Independent voltage source | $V_S = \text{constant}$                                    | $+V_S-$           | Short<br>→° ∞→    |

| Independent current source | $I_S = \text{constant}$                                    | $I_S$             | Open<br>⊸ ⊶       |

Table suggested by Richard Hester of Iowa State University.

In Table 6.2, the dc model of the resistor is a resistor, the capacitor model is an open circuit, and the inductor model is a short circuit. The forward-biased diode model includes the cut-in voltage  $V_{\gamma}$  and the forward resistance  $r_f$ .

The small-signal models of R, L, and C remain the same. However, if the signal frequency is sufficiently high, the impedance of a capacitor can be approximated by a short circuit. The small-signal, low-frequency model of the diode becomes the diode diffusion resistance  $r_d$ . Also, the independent dc voltage source becomes a short circuit, and the independent dc current source becomes an open circuit.

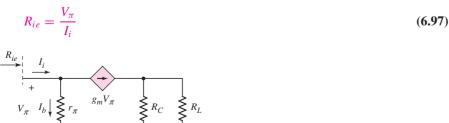

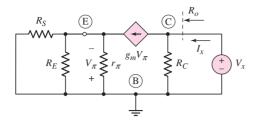

#### 6.2.3 Hybrid- $\pi$ Equivalent Circuit, Including the Early Effect

So far in the small-signal equivalent circuit, we have assumed that the collector current is independent of the collector–emitter voltage. We discussed the Early effect in the last chapter in which the collector current does vary with collector–emitter voltage. Equation (5.16) in the previous chapter gives the relation

$$i_C = I_S \left[ \exp\left(\frac{v_{BE}}{V_T}\right) \right] \cdot \left(1 + \frac{v_{CE}}{V_A}\right)$$

(5.16)

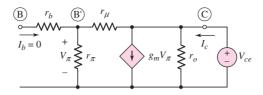

where  $V_A$  is the Early voltage and is a positive number. The equivalent circuits in Figures 6.9 and 6.10 can be expanded to take into account the Early voltage.

The output resistance  $r_o$  is defined as

$$r_o = \frac{\partial v_{CE}}{\partial i_C} \bigg|_{Q-pt}$$

(6.32)

Using Equations (5.16) and (6.32), we can write

$$\frac{1}{r_o} = \frac{\partial i_C}{\partial v_{CE}} \bigg|_{Q^- pt} = \frac{\partial}{\partial v_{CE}} \left\{ I_S \left[ \exp\left(\frac{v_{BE}}{V_T}\right) \left(1 + \frac{v_{CE}}{V_A}\right) \right] \right\} \bigg|_{Q^- pt}$$

(6.33(a))

or

$$\frac{1}{r_o} = I_S \left[ \exp\left(\frac{v_{BE}}{V_T}\right) \right] \cdot \frac{1}{V_A} \bigg|_{Q^- pt} \cong \frac{I_{CQ}}{V_A}$$

(6.33(b))

Then

$$r_o = \frac{V_A}{I_{CO}} \tag{6.34}$$

and is called the small-signal transistor output resistance.

This resistance can be thought of as an equivalent Norton resistance, which means that  $r_o$  is in parallel with the dependent current sources. Figure 6.13(a) and (b) show the modified bipolar equivalent circuits including the output resistance  $r_o$ .

**Figure 6.13** Expanded small-signal model of the BJT, including output resistance due to the Early effect, for the case when the circuit contains the (a) transconductance and (b) current gain parameters

#### EXAMPLE 6.2

**Objective:** Determine the small-signal voltage gain, including the effect of the transistor output resistance  $r_o$ .

Reconsider the circuit shown in Figure 6.3, with the parameters given in Example 6.1. In addition, assume the Early voltage is  $V_A = 50$  V.

**Solution:** The small-signal output resistance  $r_o$  is determined to be

$$r_o = \frac{V_A}{I_{CQ}} = \frac{50}{1 \text{ mA}} = 50 \text{ k}\Omega$$

Applying the small-signal equivalent circuit in Figure 6.13 to the ac equivalent circuit in Figure 6.7, we see that the output resistance  $r_o$  is in parallel with  $R_C$ . The small-signal voltage gain is therefore

$$A_{v} = \frac{V_{o}}{V_{s}} = -g_{m}(R_{C} \| r_{o}) \left(\frac{r_{\pi}}{r_{\pi} + R_{B}}\right) = -(38.5)(6\|50) \left(\frac{2.6}{2.6 + 50}\right) = -10.2$$

**Comment:** Comparing this result to that of Example 6.1, we see that  $r_o$  reduces the magnitude of the small-signal voltage gain. In many cases, the magnitude of  $r_o$  is much larger than that of  $R_c$ , which means that the effect of  $r_o$  is negligible.

#### EXERCISE PROBLEM

**Ex 6.2:** For the circuit in Figure 6.3 let  $\beta = 150$ ,  $V_A = 200$  V,  $V_{CC} = 7.5$  V,  $V_{BE}(\text{on}) = 0.7$  V,  $R_C = 15$  k $\Omega$ ,  $R_B = 100$  k $\Omega$ , and  $V_{BB} = 0.92$  V. (a) Determine the small-signal hybrid- $\pi$  parameters  $r_{\pi}$ ,  $g_m$ , and  $r_o$ . (b) Find the small-signal voltage gain  $A_v = V_o/V_s$ . (Ans. (a)  $g_m = 12.7$  mA/V,  $r_{\pi} = 11.8$  k $\Omega$ ,  $r_o = 606$  k $\Omega$  (b)  $A_v = -19.6$ )

The hybrid- $\pi$  model derives its name, in part, from the hybrid nature of the parameter units. The four parameters of the equivalent circuits shown in Figures 6.13(a) and 6.13(b) are: input resistance  $r_{\pi}$  (ohms), current gain  $\beta$  (dimensionless), output resistance  $r_o$  (ohms), and transconductance  $g_m$  (mhos).

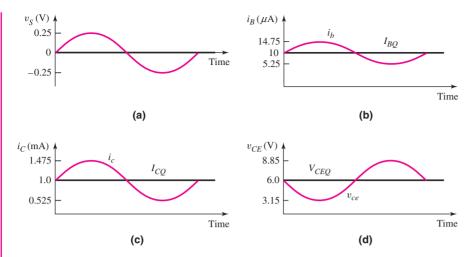

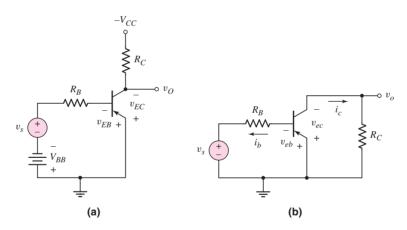

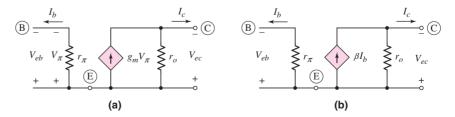

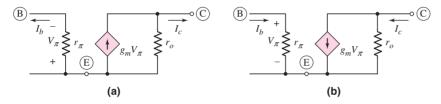

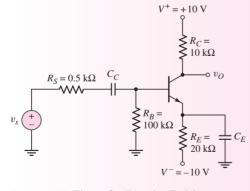

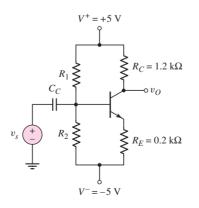

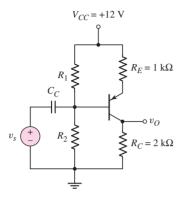

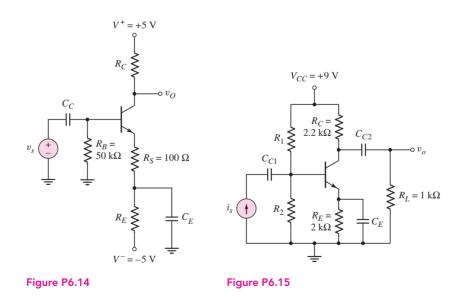

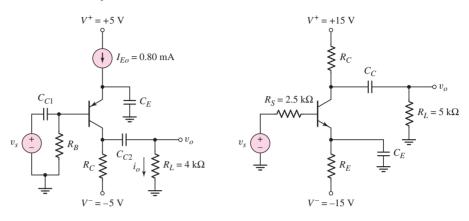

Up to this point, we have considered only circuits with npn bipolar transistors. However, the same basic analysis and equivalent circuit also applies to the pnp transistor. Figure 6.14(a) shows a circuit containing a pnp transistor. Here again, we see the change of current directions and voltage polarities compared to the circuit containing the npn transistor. Figure 6.14(b) is the ac equivalent circuit, with the dc voltage sources replaced by an ac short circuit, and all current and voltages shown are only the sinusoidal components.

The transistor in Figure 6.14(b) can now be replaced by either of the hybrid- $\pi$  equivalent circuits shown in Figure 6.15. The hybrid- $\pi$  equivalent circuit of the pnp

**Figure 6.14** (a) A common-emitter circuit with a pnp transistor and (b) the corresponding ac equivalent circuit

**Figure 6.15** The small-signal hybrid- $\pi$  equivalent circuit for the pnp transistor with the (a) transconductance and (b) current gain parameters. The ac voltage polarities and current directions are consistent with the dc parameters.

transistor is the same as that of the npn device, except that again all current directions and voltage polarities are reversed. The hybrid- $\pi$  parameters are determined by using exactly the same equations as for the npn device; that is, Equation (6.21) for  $r_{\pi}$ , Equation (6.25) for  $g_m$ , and Equation (6.34) for  $r_o$ .

We can note that, in the small-signal equivalent circuits in Figure 6.15, if we define currents of opposite direction and voltages of opposite polarity, the equivalent circuit model is exactly the same as that of the npn bipolar transistor. Figure 6.16(a) is a repeat of Figure 6.15(a) showing the conventional voltage polarities and current directions in the hybrid- $\pi$  equivalent circuit for a pnp transistor. Keep in mind that these voltages and currents are small-signal parameters. If the polarity of the input control voltage  $V_{\pi}$  is reversed, then the direction of the current from the dependent current source is also reversed. This change is shown in Figure 6.16(b). We may note that this small-signal equivalent circuit is the same as the hybrid- $\pi$ equivalent circuit for the npn transistor.

**Figure 6.16** Small-signal hybrid- $\pi$  models of the pnp transistor: (a) original circuit shown in Figure 6.15 and (b) equivalent circuit with voltage polarities and current directions reversed

However, the author prefers to use the models shown in Figure 6.15 because the current directions and voltage polarities are consistent with the pnp device.

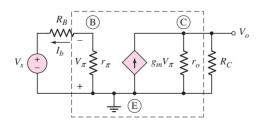

Combining the hybrid- $\pi$  model of the pnp transistor (Figure 6.15(a)) with the ac equivalent circuit (Figure 6.14(b)), we obtain the small-signal equivalent circuit shown in Figure 6.17. The output voltage is given by

$$V_o = (g_m V_\pi)(r_o || R_C)$$

(6.35)

The control voltage  $V_{\pi}$  can be expressed in terms of the input signal voltage  $V_s$  using a voltage divider equation. Taking into account the polarity, we find

$$V_{\pi} = -\frac{V_s r_{\pi}}{R_B + r_{\pi}} \tag{6.36}$$

**Figure 6.17** The small-signal equivalent circuit of the common-emitter circuit with a pnp transistor. The small-signal hybrid- $\pi$  equivalent circuit model of the pnp transistor is shown within the dashed lines.

Combining Equations (6.35) and (6.36), we obtain the small-signal voltage gain:

$$A_{v} = \frac{V_{o}}{V_{s}} = \frac{-g_{m}r_{\pi}}{R_{B} + r_{\pi}}(r_{o} || R_{C}) = \frac{-\beta}{R_{B} + r_{\pi}}(r_{o} || R_{C})$$

(6.37)

The expression for the small-signal voltage gain of the circuit containing a pnp transistor is exactly the same as that for the npn transistor circuit. Taking into account the reversed current directions and voltage polarities, the voltage gain still contains a negative sign indicating a 180-degree phase shift between the input and output signals.

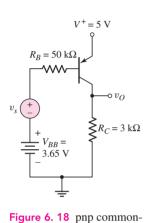

#### EXAMPLE 6.3

Objective: Analyze a pnp amplifier circuit.

Consider the circuit shown in Figure 6.18. Assume transistor parameters of  $\beta = 80$ ,  $V_{EB}(\text{on}) = 0.7$  V, and  $V_A = \infty$ .

Solution (DC Analysis): A dc KVL equation around the E-B loop yields

$$V^+ = V_{EB}(\text{on}) + I_{BQ}R_B + V_{BB}$$

or

$5 = 0.7 + I_{BO}(50) + 3.65$

which yields

$$I_{BO} = 13 \ \mu \text{A}$$

Then

$I_{CO} = 1.04 \text{ mA}$   $I_{EO} = 1.05 \text{ mA}$

A dc KVL equation around the E-C loop yields

$$V^+ = V_{ECO} + I_{CO}R_0$$

or

$$5 = V_{ECO} + (1.04)(3)$$

We find

$$V_{ECO} = 1.88 \text{ V}$$

The transistor is therefore biased in the forward-active mode.

**Solution (AC Analysis):** The small-signal hybrid- $\pi$  parameters are found to be

$$g_m = \frac{I_{CQ}}{V_T} = \frac{1.04}{0.026} = 40 \text{ mA/V}$$

$$r_\pi = \frac{\beta V_T}{I_{CQ}} = \frac{(80)(0.026)}{1.04} = 2 \text{ k}\Omega$$

and

$$r_o = \frac{V_A}{I_{CQ}} = \frac{\infty}{1.04} = \infty$$

The small-signal equivalent circuit is the same as shown in Figure 6.17. With  $r_o = \infty$ , the small-signal output voltage is

$$V_o = (g_m V_\pi) R_C$$

emitter circuit for

Example 6.3

and we have

$$V_{\pi} = -\left(\frac{r_{\pi}}{r_{\pi} + R_B}\right) \cdot V_s$$

Noting that  $\beta = g_m r_{\pi}$ , we find the small-signal voltage gain to be

$$A_v = \frac{V_o}{V_s} = \frac{-\beta R_C}{r_\pi + R_B} = \frac{-(80)(3)}{2+50}$$

or

$A_v = -4.62$

**Comment:** We again note the  $-180^{\circ}$  phase shift between the output and input signals. We may also note that the base resistance  $R_B$  in the denominator substantially reduces the magnitude of the small-signal voltage gain. We can also note that placing the pnp transistor in this configuration allows us to use positive power supplies.

#### **EXERCISE PROBLEM**

**Ex 6.3:** For the circuit in Figure 6.14(a), let  $\beta = 90$ ,  $V_A = 120$  V,  $V_{CC} = 5$  V,  $V_{EB}(\text{on}) = 0.7$  V,  $R_C = 2.5$  k $\Omega$ ,  $R_B = 50$  k $\Omega$ , and  $V_{BB} = 1.145$  V. (a) Determine the small-signal hybrid- $\pi$  parameters  $r_{\pi}$ ,  $g_m$ , and  $r_o$ . (b) Find the small-signal voltage gain  $A_v = V_o/V_s$ . (Ans. (a)  $g_m = 30.8$  mA/V,  $r_{\pi} = 2.92$  k $\Omega$ ,  $r_o = 150$  k $\Omega$  (b)  $A_v = -4.18$ )

## **Test Your Understanding**

**TYU 6.1** A BJT with  $\beta = 120$  and  $V_A = 150$  V is biased such that  $I_{CQ} = 0.25$  mA. Determine  $g_m$ ,  $r_\pi$ , and  $r_o$ . (Ans.  $g_m = 9.62$  mA/V,  $r_\pi = 12.5$  k $\Omega$ ,  $r_o = 600$  k $\Omega$ )

**TYU 6.2** The Early voltage of a BJT is  $V_A = 75$  V. Determine the minimum required collector current such that the output resistance is at least  $r_o = 200$  k $\Omega$ . (Ans.  $I_{CQ} = 0.375$  mA)

#### \*6.2.4 Expanded Hybrid- $\pi$ Equivalent Circuit

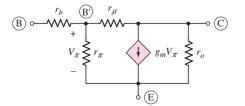

Figure 6.19 shows an expanded hybrid- $\pi$  equivalent circuit, which includes two additional resistances,  $r_b$  and  $r_{\mu}$ .

Figure 6.19 Expanded hybrid- $\pi$  equivalent circuit

<sup>\*</sup>Sections can be skipped without loss of continuity.

The parameter  $r_b$  is the series resistance of the semiconductor material between the external base terminal B and an idealized internal base region B'. Typically,  $r_b$  is a few tens of ohms and is usually much smaller than  $r_{\pi}$ ; therefore,  $r_{h}$  is normally negligible (a short circuit) at low frequencies. However, at high frequencies,  $r_h$  may not be negligible, since the input impedance becomes capacitive, as we will see in Chapter 7.

The parameter  $r_{\mu}$  is the **reverse-biased diffusion resistance** of the base–collector junction. This resistance is typically on the order of megohms and can normally be neglected (an open circuit). However, the resistance does provide some feedback between the output and input, meaning that the base current is a slight function of the collector-emitter voltage.

In this text, when we use the hybrid- $\pi$  equivalent circuit model, we will neglect both  $r_b$  and  $r_{\mu}$ , unless they are specifically included.

#### **Other Small-Signal Parameters** \*6.2.5 and Equivalent Circuits

Other small-signal parameters can be developed to model the bipolar transistor or other transistors described in the following chapters.

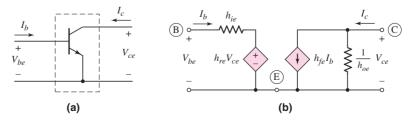

One common equivalent circuit model for bipolar transistor uses the *h*parameters, which relate the small-signal terminal currents and voltages of a twoport network. These parameters are normally given in bipolar transistor data sheets, and are convenient to determine experimentally at low frequency.

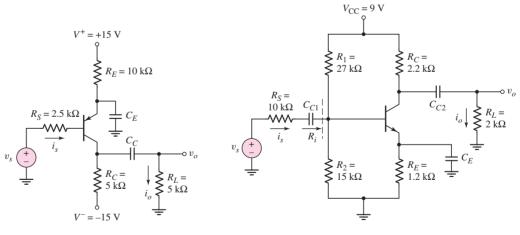

Figure 6.20(a) shows the small-signal terminal current and voltage phasors for a common-emitter transistor. If we assume the transistor is biased at a *Q*-point in the forward-active region, the linear relationships between the small-signal terminal currents and voltages can be written as

$$V_{be} = h_{ie}I_b + h_{re}V_{ce}$$

(6.38(a))

$$I_c = h_{fe}I_b + h_{oe}V_{ce} \tag{6.38(b)}$$

These are the defining equations of the common–emitter *h*-parameters, where the subscripts are: *i* for input, *r* for reverse, *f* for forward, *o* for output, and *e* for common emitter.

These equations can be used to generate the small-signal h-parameter equivalent circuit, as shown in Figure 6.20(b). Equation (6.38(a)) represents a Kirchhoff voltage law equation at the input, and the resistance  $h_{ie}$  is in series with a dependent voltage source equal to  $h_{re}V_{ce}$ . Equation (6.38(b)) represents a Kirchhoff current law equation at the output, and the conductance  $h_{oe}$  is in parallel with a dependent current source equal to  $h_{fe}I_b$ .

Figure 6.20 (a) Common-emitter npn transistor and (b) the *h*-parameter model of the common-emitter bipolar transistor

Figure 6.21 Expanded hybrid- $\pi$  equivalent circuit with the output short-circuited

Since both the hybrid- $\pi$  and *h*-parameters can be used to model the characteristics of the same transistor, these parameters are not independent. We can relate the hybrid- $\pi$  and *h*-parameters using the equivalent circuit shown in Figure 6.19. The **small-signal input resistance**  $h_{ie}$ , from Equation (6.38(a)), can be written as

$$h_{ie} = \frac{V_{be}}{I_b} \bigg|_{V_{ce}=0}$$

(6.39)

where the small-signal C–E voltage is held at zero. With the C–E voltage equal to zero, the circuit in Figure 6.19 is transformed to the one shown in Figure 6.21. From this figure, we see that

$$h_{ie} = r_b + r_\pi \| r_\mu \tag{6.40}$$

In the limit of a very small  $r_b$  and a very large  $r_{\mu}$ ,  $h_{ie} \cong r_{\pi}$ .

The parameter  $h_{fe}$  is the **small-signal current gain.** From Equation (6.38(b)), this parameter can be written as

$$h_{fe} = \frac{I_c}{I_b}\Big|_{V_{ce}=0}$$

(6.41)

Since the collector–emitter voltage is again zero, we can use Figure 6.21, for which the short-circuit collector current is

$$I_c = g_m V_\pi \tag{6.42}$$

If we again consider the limit of a very small  $r_b$  and a very large  $r_{\mu}$ , then

$$V_{\pi} = I_b r_{\pi}$$

and

$$h_{fe} = \frac{I_c}{I_b}\Big|_{V_{ce}=0} = g_m r_\pi = \beta$$

(6.43)

Consequently, at low frequency, the small-signal current gain  $h_{fe}$  is essentially equal to  $\beta$  in most situations.

The parameter  $h_{re}$  is called the **voltage feedback ratio**, which, from Equation (6.38(a)), can be written as

$$h_{re} = \frac{V_{be}}{V_{ce}}\Big|_{I_b=0}$$

(6.44)

Since the input signal base current is zero, the circuit in Figure 6.19 transformed to that shown in Figure 6.22, from which we can see that

$$V_{be} = V_{\pi} = \left(\frac{r_{\pi}}{r_{\pi} + r_{\mu}}\right) \cdot V_{ce}$$

(6.45(a))

**Figure 6.22** Expanded hybrid- $\pi$  equivalent circuit with the input open-circuited

and

$$h_{re} = \frac{V_{be}}{V_{ce}} \bigg|_{I_{b}=0} = \frac{r_{\pi}}{r_{\pi} + r_{\mu}}$$

(6.45(b))

Since  $r_{\pi} \ll r_{\mu}$ , this can be approximated as

$$h_{re} \cong \frac{r_{\pi}}{r_{\mu}} \tag{6.46}$$

Since  $r_{\pi}$  is normally in the kilohm range and  $r_{\mu}$  is in the megohm range, the value of  $h_{re}$  is very small and can usually be neglected.

The fourth *h*-parameter is the **small-signal output admittance**  $h_{oe}$ . From Equation (6.38(b)), we can write

$$h_{oe} = \frac{I_c}{V_{ce}} \Big|_{I_b=0}$$

(6.47)

Since the input signal base current is again set equal to zero, the circuit in Figure 6.22 is applicable, and a Kirchhoff current law equation at the output node produces

$$I_c = g_m V_\pi + \frac{V_{ce}}{r_o} + \frac{V_{ce}}{r_\pi + r_\mu}$$

(6.48)

where  $V_{\pi}$  is given by Equation (6.45(a)). For  $r_{\pi} \ll r_{\mu}$ , Equation (6.48) becomes

$$h_{oe} = \frac{I_c}{V_{ce}} \Big|_{I_b=0} = \frac{1+\beta}{r_{\mu}} + \frac{1}{r_o}$$

(6.49)

In the ideal case,  $r_{\mu}$  is infinite, which means that  $h_{oe} = 1/r_o$ .

The *h*-parameters for a pnp transistor are defined in the same way as those for an npn device. Also, the small-signal equivalent circuit for a pnp transistor using *h*-parameters is identical to that of an npn device, except that the current directions and voltage polarities are reversed.

#### EXAMPLE 6.4

**Objective:** Determine the *h*-parameters of a specific transistor.

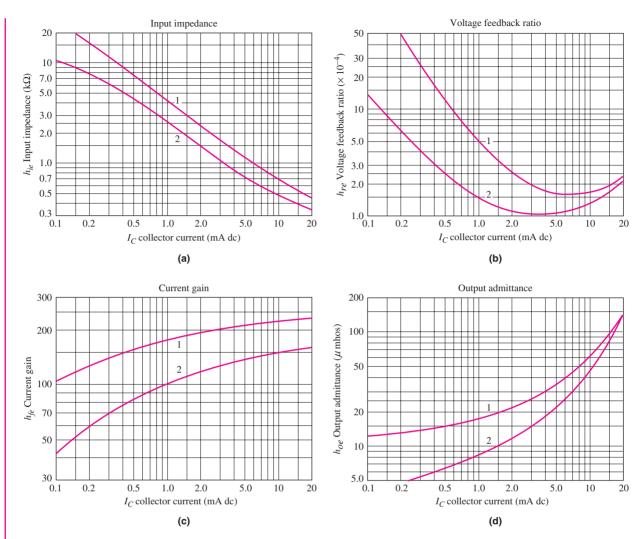

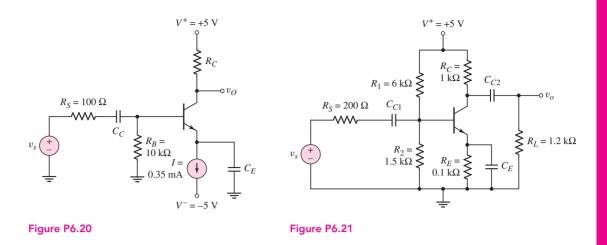

The 2N2222A transistor is a commonly used discrete npn transistor. Data for this transistor are shown in Figure 6.23. Assume the transistor is biased at  $I_C = 1$  mA and let T = 300 K.

**Solution:** In Figure 6.23, we see that the small-signal current gain  $h_{fe}$  is generally in the range  $100 < h_{fe} < 170$  for  $I_C = 1$  mA, and the corresponding value of  $h_{ie}$  is generally between 2.5 and 5 k $\Omega$ . The voltage feedback ratio  $h_{re}$  varies between

**Figure 6.23** *h*-parameter data for the 2N2222A transistor. Curves 1 and 2 represent data from high-gain and low-gain transistors, respectively.

$1.5 \times 10^{-4}$  and  $5 \times 10^{-4}$ , and the output admittance  $h_{oe}$  is in the range  $8 < h_{oe} < 18 \,\mu$ mhos.

**Comment:** The purpose of this example is to show that the parameters of a given transistor type can vary widely. In particular, the current gain parameter can easily vary by a factor of two. These variations are due to tolerances in the initial semiconductor properties and in the production process variables.

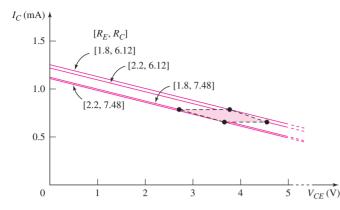

**Design Pointer:** This example clearly shows that there can be a wide variation in transistor parameters. Normally, a circuit is designed using nominal parameter values, but the allowable variations must be taken into account. In Chapter 5, we noted how a variation in  $\beta$  affects the *Q*-point. In this chapter, we will see how the variations in small-signal parameters affect the small-signal voltage gain and other characteristics of a linear amplifier.

#### EXERCISE PROBLEM

**Ex 6.4:** Repeat Example 6.4 if the quiescent collector current is (a)  $I_{CQ} = 0.2 \text{ mA}$ and (b)  $I_{CQ} = 5 \text{ mA}$ . [Ans. (a)  $7.8 < h_{ie} < 15 \text{ k}\Omega$ ,  $6.2 \times 10^{-4} < h_{re} < 50 \times 10^{-4}$ ,  $60 < h_{fe} < 125$ ,  $5 < h_{oe} < 13 \mu \text{mhos}$ ; (b)  $0.7 < h_{ie} < 1.1 \text{ k}\Omega$ ,  $1.05 \times 10^{-4} < h_{re} < 1.6 \times 10^{-4}$ ,  $140 < h_{fe} < 210$ ,  $22 < h_{oe} < 35 \mu \text{mhos}$ )

In the previous discussion, we indicated that the *h*-parameters  $h_{ie}$  and  $1/h_{oe}$  are essentially equivalent to the hybrid- $\pi$  parameters  $r_{\pi}$  and  $r_o$ , respectively, and that  $h_{fe}$  is essentially equal to  $\beta$ . The transistor circuit response is independent of the transistor model used. This reinforces the concept of a relationship between hybrid- $\pi$  parameters and *h*-parameters. In fact, this is true for any set of small-signal parameters; that is, any given set of small-signal parameters is related to any other set of parameters.

#### **Data Sheet**

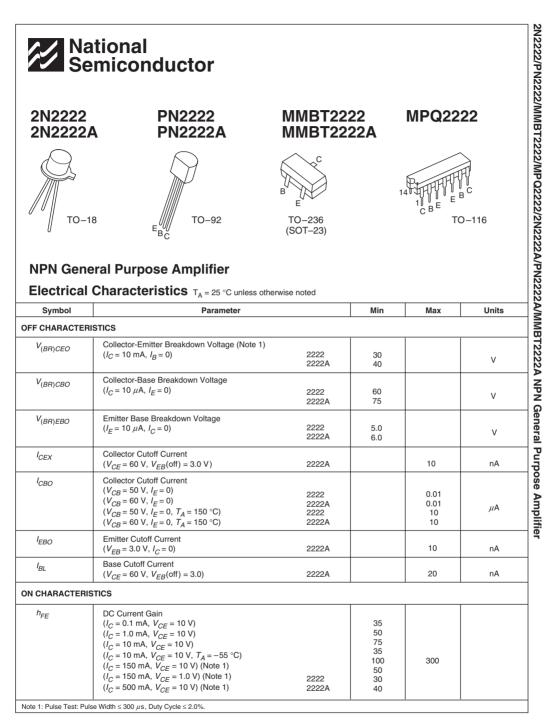

In the previous example, we showed some data for the 2N2222 discrete transistor. Figure 6.24 shows additional data from the data sheet for this transistor. Data sheets contain a lot of information, but we can begin to discuss some of the data at this time.

The first set of parameters pertains to the transistor in cutoff. The first two parameters listed are  $V_{(BR)CEO}$  and  $V_{(BR)CBO}$ , which are the collector–emitter breakdown voltage with the base terminal open and the collector–base breakdown voltage with the emitter open. These parameters were discussed in Section 5.1.6 in the last chapter. In that section, we argued that  $V_{(BR)CBO}$  was larger than  $V_{(BR)CEO}$ , which is supported by the data shown. These two voltages are measured at a specific current in the breakdown region. The third parameter,  $V_{(BR)EBO}$ , is the emitter–base breakdown voltage, which is substantially less than the collector–base or collector–emitter breakdown voltages.

The current  $I_{CBO}$  is the reverse-biased collector-base junction current with the emitter open ( $I_E = 0$ ). This parameter was also discussed in Section 5.1.6. In the data sheet, this current is measured at two values of collector-base voltage and at two temperatures. The reverse-biased current increases with increasing temperature, as we would expect. The current  $I_{EBO}$  is the reverse-biased emitter-base junction current with the collector open ( $I_C = 0$ ). This current is also measured at a specific reverse-biase voltage. The other two current parameters,  $I_{CEX}$  and  $I_{BL}$ , are the collector current and base current measured at given specific cutoff voltages.

The next set of parameters applies to the transistor when it is turned on. As was shown in Example 6.4, the data sheets give the *h*-parameters of the transistor. The first parameter,  $h_{FE}$ , is the dc common-emitter current gain and is measured over a wide range of collector current. We discussed, in Section 5.4.2, stabilizing the *Q*-point against variations in current gain. The data presented in the data sheet show that the current gain for a given transistor can vary significantly, so that stabilizing the *Q*-point is indeed an important issue.

We have used  $V_{CE}(\text{sat})$  as one of the piecewise linear parameters when a transistor is driven into saturation and have always assumed a particular value in our analysis or design. This parameter, listed in the data sheet, is not a constant but varies with collector current. If the collector becomes relatively large, then the collector– emitter saturation voltage also becomes relatively large. The larger  $V_{CE}(\text{sat})$  value would need to be taken into account in large-current situations. The base–emitter voltage for a transistor driven into saturation,  $V_{BE}(\text{sat})$ , is also given. Up to this point

395

Figure 6.24 Basic data sheet for the 2N2222 bipolar transistor

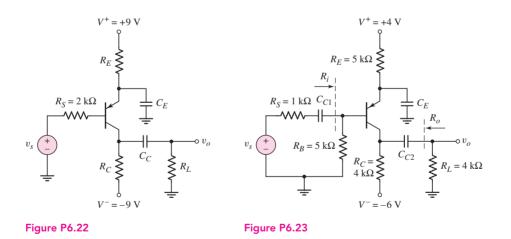

|                       |                                                                                                                                      | Parameter                                                                                                   |                                        | Min        | Max                      | Uni |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------|------------|--------------------------|-----|

| ON CHARACT            | ERISTICS (Continued)                                                                                                                 |                                                                                                             |                                        |            |                          |     |

| V <sub>CE</sub> (sat) | Collector-Emitter Saturation Vol<br>( $I_C = 150$ mA, $I_B = 15$ mA)<br>( $I_C = 500$ mA, $I_B = 50$ mA)                             | tage (Note 1)                                                                                               | 2222<br>2222A<br>2222<br>2222<br>2222A |            | 0.4<br>0.3<br>1.6<br>1.0 | v   |

| V <sub>BE</sub> (sat) | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                             |                                                                                                             |                                        | 0.6<br>0.6 | 1.3<br>1.2<br>2.6<br>2.0 | v   |

| SMALL-SIGN            | AL CHARACTERISTICS                                                                                                                   |                                                                                                             |                                        |            |                          |     |

| f <sub>T</sub>        | Current Gain—Bandwidth Produ<br>$(I_C = 20 \text{ mA}, V_{CE} = 20 \text{ V}, f = 100)$                                              |                                                                                                             | 2222<br>2222A                          | 250<br>300 |                          | мн  |

| C <sub>obo</sub>      | Output Capacitance (Note 3)<br>( $V_{CB} = 10 \text{ V}, I_E = 0, f = 100 \text{ kHz}$ )                                             |                                                                                                             |                                        |            | 8.0                      | pF  |

| C <sub>ibo</sub>      |                                                                                                                                      |                                                                                                             | 2222<br>2222A                          |            | 30<br>25                 | pF  |

| rb'C <sub>C</sub>     | Collector Base Time Constant<br>( $I_E = 20 \text{ mA}, V_{CB} = 20 \text{ V}, f = 31.8 \text{ MHz}$ )                               |                                                                                                             | 2222A                                  |            | 150                      | ps  |

| NF                    | Noise Figure<br>( $I_C$ = 100 μA, $V_{CE}$ = 10 V, $R_S$ = 1.0 kΩ, f = 1.0 kHz)                                                      |                                                                                                             | 2222A                                  |            | 4.0                      | dE  |

| $Re(h_{ie})$          | Real Part of Common-Emitter<br>High Frequency Input Impedance<br>$(I_C = 20 \text{ mA}, V_{CE} = 20 \text{ V}, f = 300 \text{ MHz})$ |                                                                                                             |                                        |            | 60                       | Ω   |

| SWITCHING C           | HARACTERISTICS                                                                                                                       |                                                                                                             |                                        |            |                          |     |

| t <sub>D</sub>        | Delay Time                                                                                                                           | $(V_{CC} = 30 \text{ V}, V_{PE}(\text{off}) = 0.5 \text{ V}.$                                               | except                                 |            | 10                       | ns  |

| t <sub>R</sub>        | Rise Time                                                                                                                            | $(V_{CC} = 30 \text{ V}, V_{BE}(\text{off}) = 0.5 \text{ V}, I_C = 150 \text{ mA}, I_{B1} = 15 \text{ mA})$ | MPQ2222                                |            | 25                       | ns  |

| t <sub>S</sub>        | Storage Time                                                                                                                         | $(V_{aa} = 30 \text{ V} / a = 150 \text{ mA}$                                                               | except                                 |            | 225                      | ns  |

| t <sub>F</sub>        | Fall Time                                                                                                                            | $(V_{CC} = 30 \text{ V}, I_C = 150 \text{ mA}, I_{B1} = I_{B2} = 15 \text{ mA})$                            | MPQ2222                                |            | 60                       | ns  |

Figure 6.24 (continued)

in the text, we have not been concerned with this parameter; however, the data sheet shows that the base–emitter voltage can increase significantly when a transistor is driven into saturation at high current levels.

The other parameters listed in the data sheet become more applicable later in the text when the frequency response of transistors is discussed. The intent of this short discussion is to show that we can begin to read through data sheets even though there are a lot of data presented.

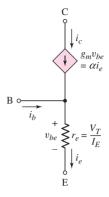

**The T-model:** The hybrid-pi model can be used to analyze the time-varying characteristics of all transistor circuits. We have briefly discussed the h-parameter model of the transistor. The h-parameters of this model are often given in data sheets for discrete transistors. Another small-signal model of the transistor, the T-model, is shown in Figure 6.25. This model might be convenient to use in specific applications. However, to avoid introducing too much confusion, we will concentrate on using the hybrid-pi model in this text and leave the T-model to more advanced electronics courses.

Figure 6.25 The T-model of an npn bipolar transistor

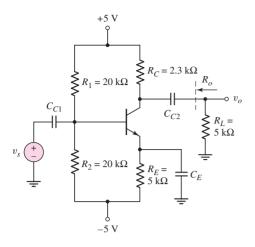

## 6.3 BASIC TRANSISTOR AMPLIFIER CONFIGURATIONS

**Objective:** • Discuss the three basic transistor amplifier configurations and discuss the four equivalent two-port networks.

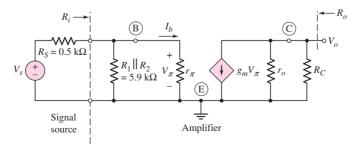

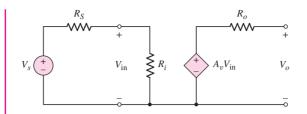

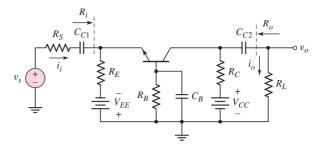

As we have seen, the bipolar transistor is a three-terminal device. Three basic singletransistor amplifier configurations can be formed, depending on which of the three transistor terminals is used as signal ground. These three basic configurations are appropriately called **common emitter, common collector (emitter follower),** and **common base.** Which configuration or amplifier is used in a particular application depends to some extent on whether the input signal is a voltage or current and whether the desired output signal is a voltage or current. The characteristics of the three types of amplifiers will be determined to show the conditions under which each amplifier is most useful.

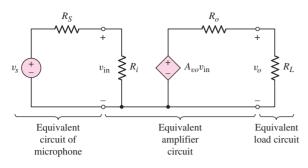

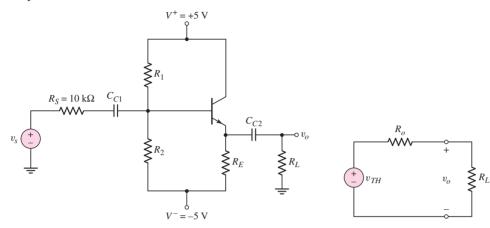

The input signal source can be modeled as either a Thevenin or Norton equivalent circuit. Figure 6.26(a) shows the Thevenin equivalent source that would represent a voltage signal, such as the output of a microphone. The voltage source  $v_s$ represents the voltage generated by the microphone. The resistance  $R_s$  is called the output resistance of the source and takes into account the change in output voltage as the source supplies current. Figure 6.26(b) shows the Norton equivalent source that

Figure 6.26. Input signal source modeled as (a) Thevenin equivalent circuit and (b) Norton equivalent circuit

| Table 6.3         Four equivalent two-port networks |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |  |  |  |

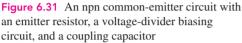

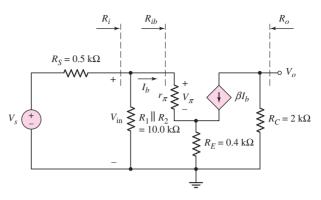

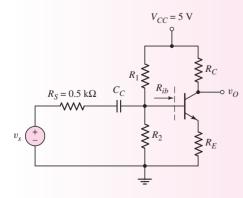

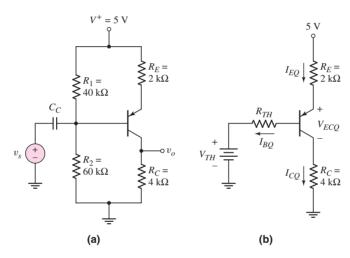

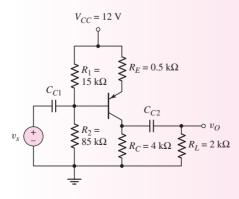

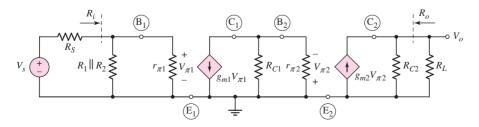

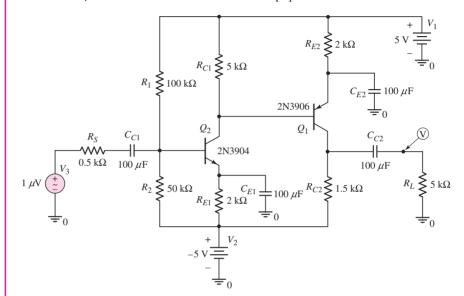

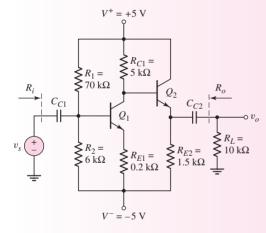

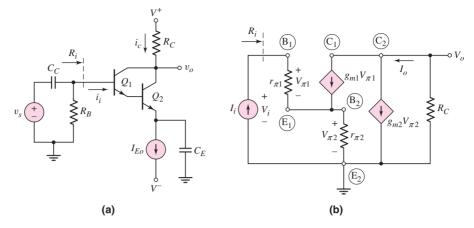

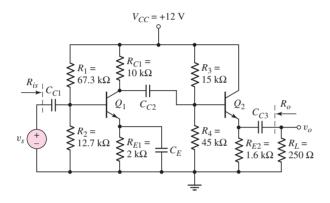

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|