Session 1: Trends in VLSI

# Solid State Devices

### **Course Objective**

• We will study collection of semiconductor devices. From Transistors to optoelectronic devices.

- There will be project/homework with Silvaco

- $_{\odot}$  There is no single Textbook for the course

$\circ~$  Most of the material (books, papers) needed for this course will be provided

- Lecture Notes: combination of slides and discussions

- -- Slides will be posted on the class webpage

- -- http://ee.sharif.edu/~sarvari/Teaching.html

## **Required Text/Reference Material**

Kwok K. Ng, "Complete Guide to Semiconductor Devices", 2nd Ed., 2002

Brennan and Brown, "Theory of Modern Electronic Semiconductor Devices", 2002

- Sze and Ng," Physics of Semiconductor Devices", 3rd Ed., 2006

- Taur and Ning, "Fundamentals of Modern VLSI Devices", 2009

Mishra and Singh, "Semiconductor Device Physics and Design", 2008

- Roblin and Rohdin, "High-speed Heterostructure Devices", 2002

- Singh, "Semiconductor Optoelectronics", 1995

- Selected research papers from the literature

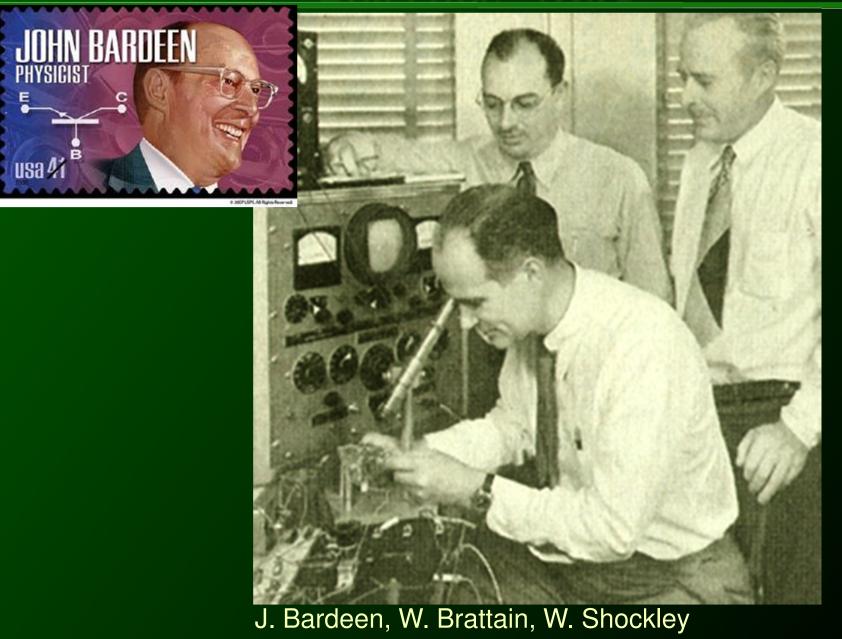

The 1946 ENIAC computer used 17,468 vacuum tubes and consumed 150kW of power

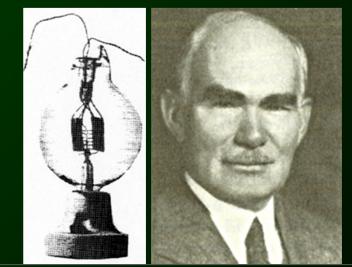

#### Lee De Forest (1873 – 1961)

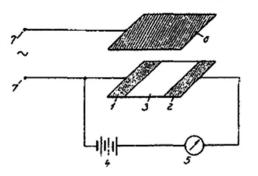

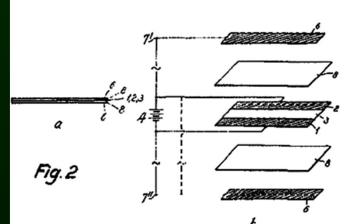

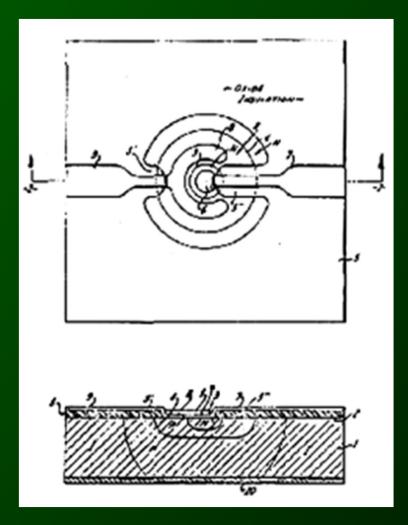

#### **Field Effect Transistor**

SILM

#### Julius Edgar Lilienfeld (1882 –1963)

#### Oskar Heil (1908 – 1994)

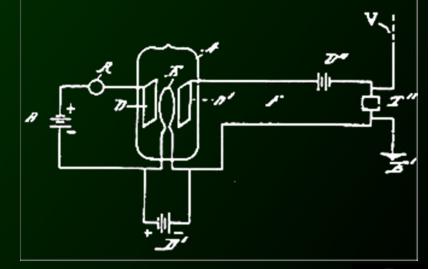

**DEVICES FOR** CONTROLLED ELECTRIC CURRENT, Filed March 28, 1928

Patented Mar. 7, 1933 1,900,018 UNITED STATES PATENT OFFICE FULFUS EDGAR LILIENFELD, OF BROOKLYN, NEW YORK DEVICE FOR CONTROLLING ELECTRIC CORRENT Application Erd March 18, 1936. Serial No. 143,375. J. E. LILIENFELD DEVICE FOR CONTROLLING ELECTRIC CURRENT Cu25 Filed March 28. 1928 3 Sheets-Sheet 1 H Alverry Ouide Aluminum "G Grig.2. D

∙G

British patent of 1935

Fig. 1

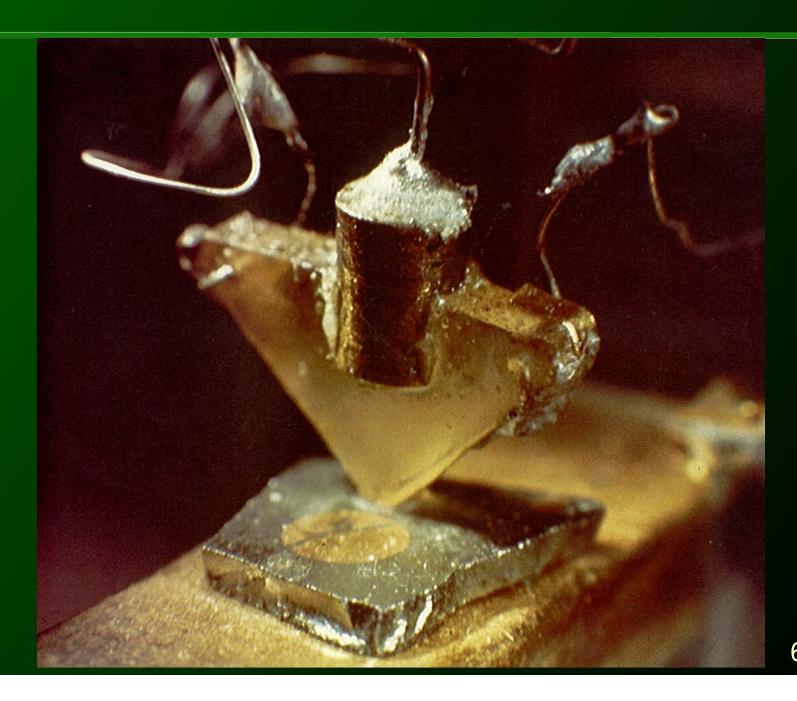

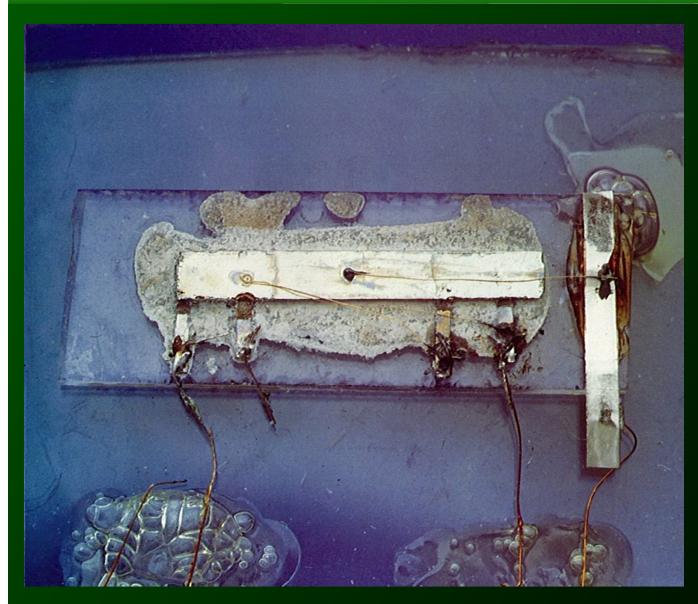

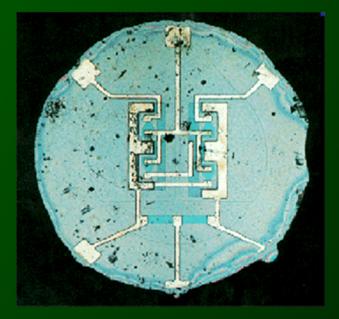

## 1958, Kilby, Texas Instruments

Jack St. Clair Kilby (1923 – 2005)

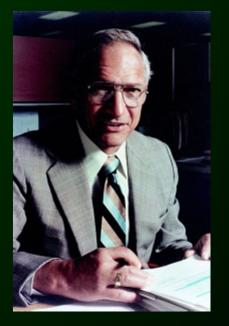

### 1960, Noyce, planar integrated circuit

Robert Norton Noyce(1927 – 1990)

Co-founder of Fairchild Semiconductor and Intel

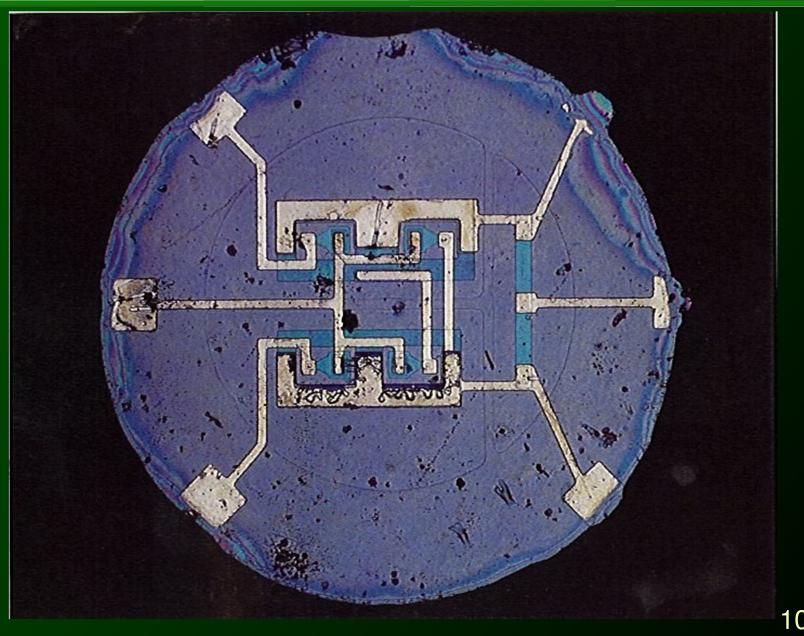

## Early IC - Fairchild

## 1960, MOSFET, D. Kahng and M. Atalla

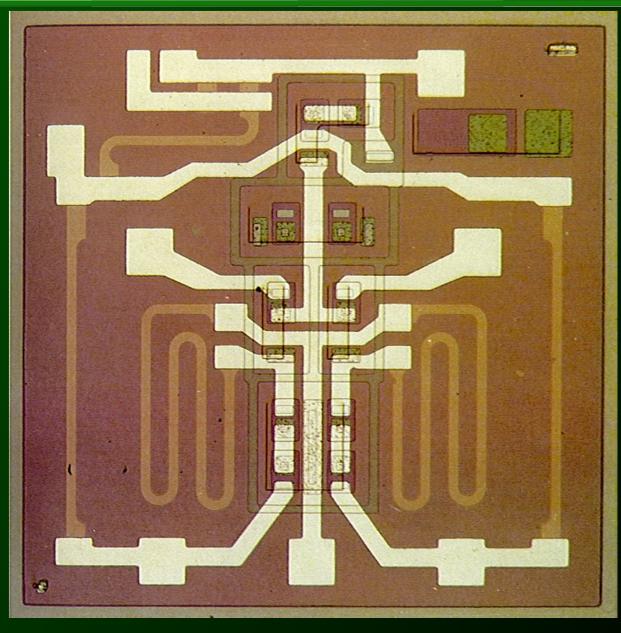

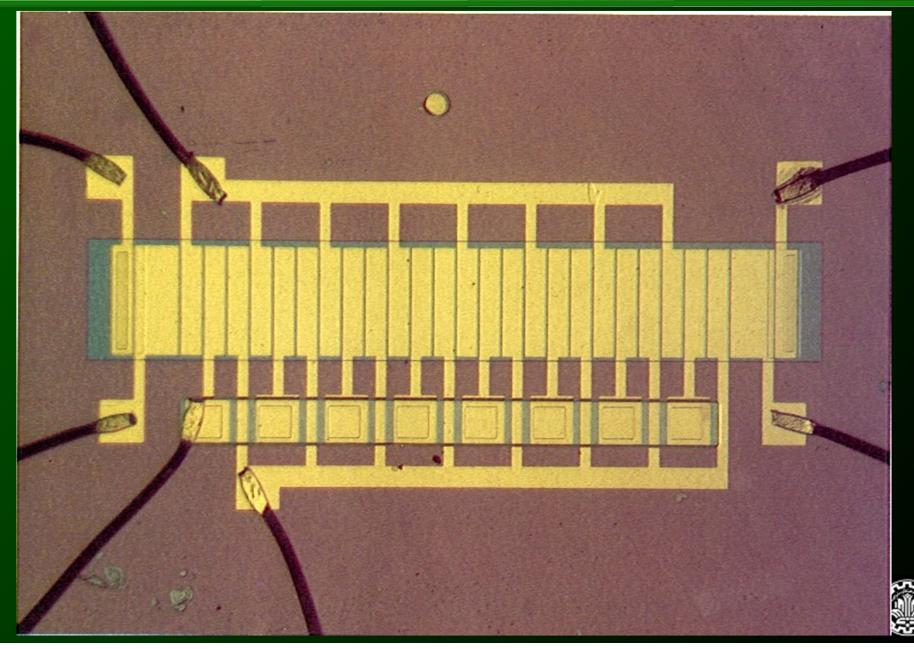

### 1964 - Op-Amp uA702, Fairchild

#### 1965 - Op-Amp uA709, Fairchild

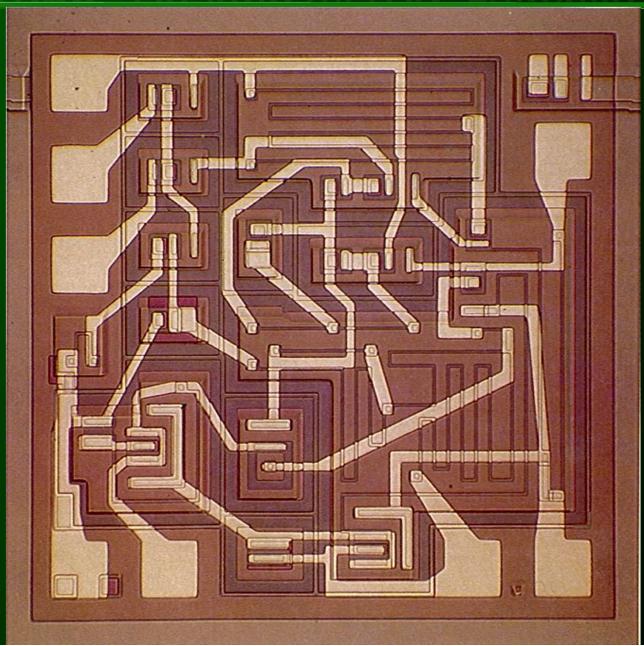

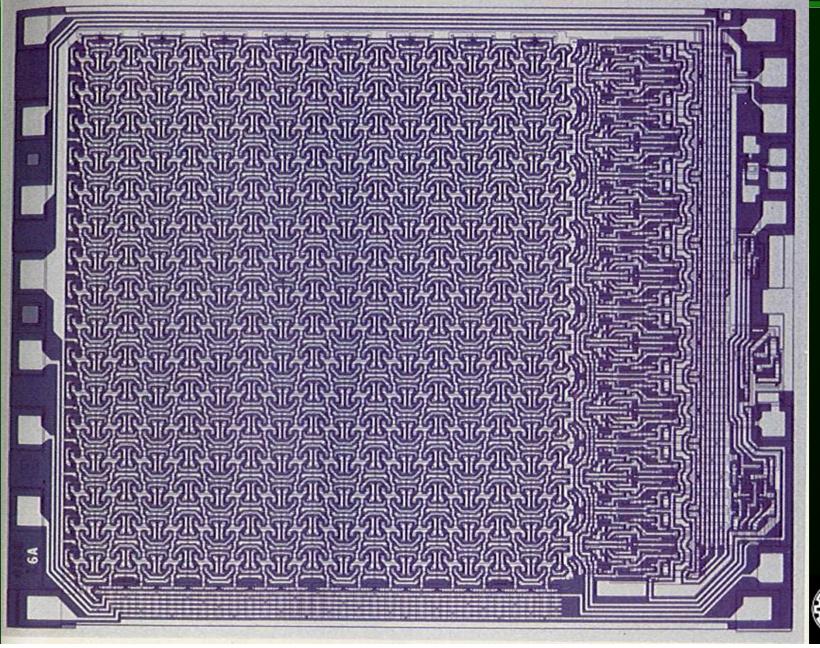

#### 1970 - 1024 Bit DRAM, Intel

## 1970 - CCD 8 Bit, Bell Labs

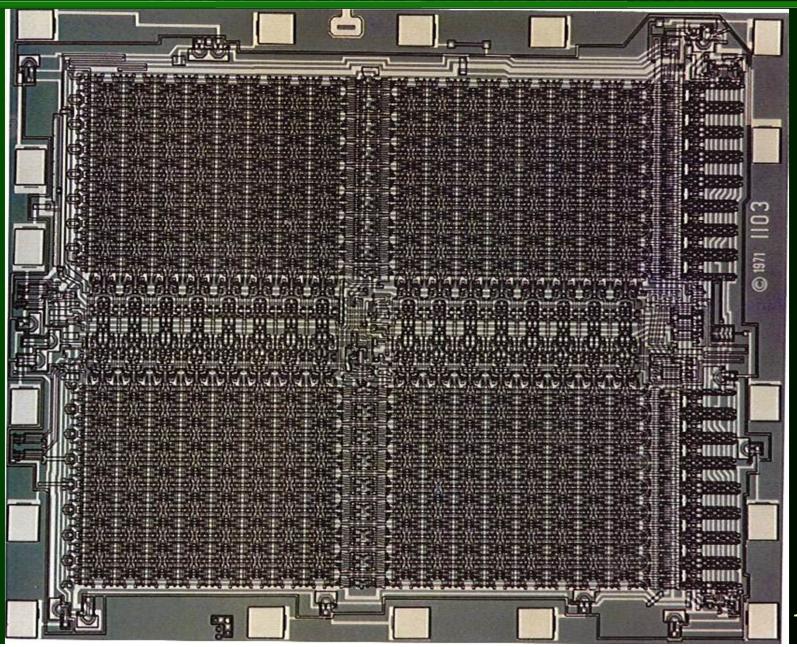

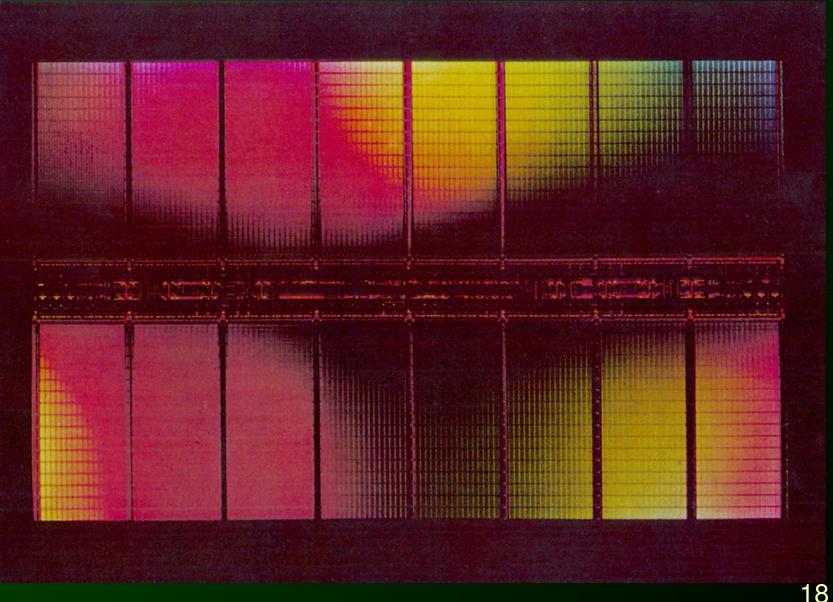

## 2001 - 256Mbit DRAM , TOSHIBA

### Circuits: from 1961 to 2005

The first planar integrated circuit, 1960.

Designed and built by Lionel Kattner and Isy Haas under the direction of Jay Last at Fairchild Semiconductor.

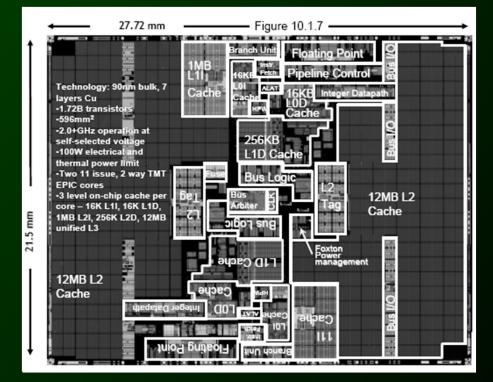

The Intel "Montecito" microprocessor, 2005

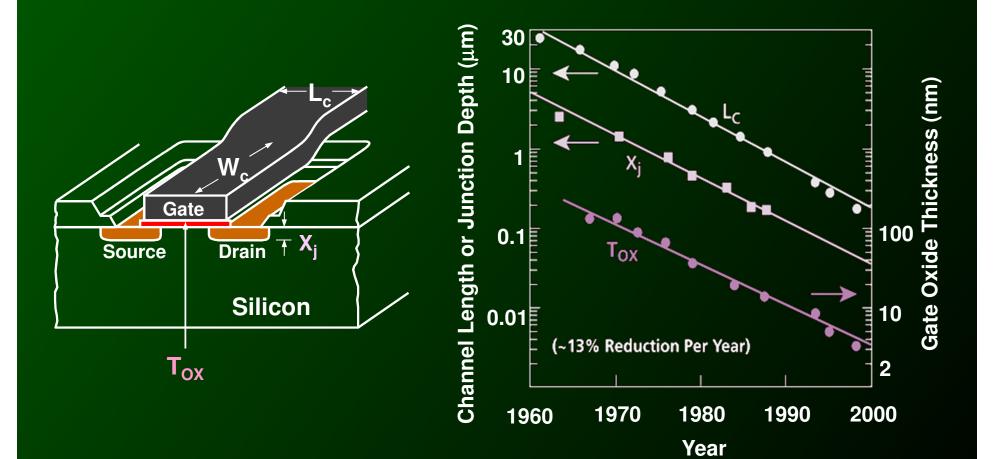

### Scaling of MOSFET Dimensions

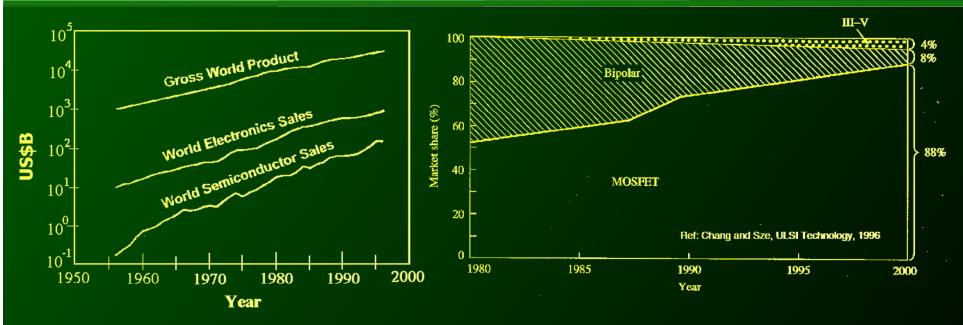

#### Trends in Semiconductor/CMOS Market

Semiconductors have become increasingly more important part of world economy

In 2000: 0.7% of GWP Today: 5% of GWP CMOS has become the pervasive technology

### Intriguing ... but Challenging

#### Challenges:

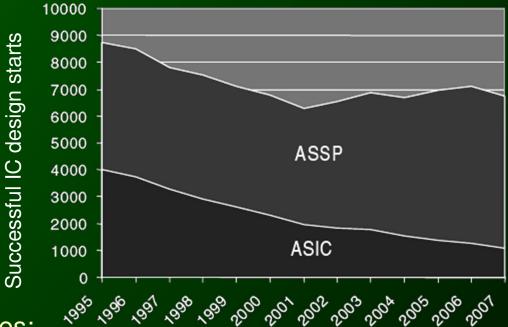

- The NRE cost of IC manufacturing (about 2M\$ for mask)

- Deep-submicron effects

- Complexity (100 million transistors)

- Power and Energy

- Reliability and Robustness

- Beyond Silicon!

ASSP is an integrated circuit that implements a specific function that appeals to a wide market. As opposed to ASICs that combine a collection of functions and designed by or for one customer

## Interconnect?

2 Major problems facing Moore's law:

- Power dissipation

- Interconnects

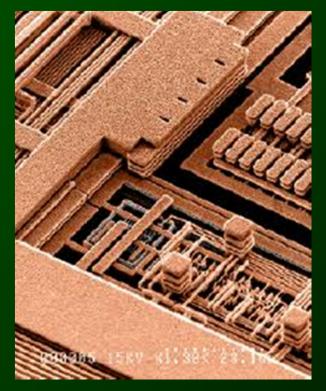

#### IBM Cu technology

#### from IBM Cross-section of 64-bit highperformance microprocessor

## **Connectivity and Complexity**

#### Challenge of System Complexity

### NoC Network-on-a-Chip

Traditional communication techniques: point-to-point connection, busses

The wires occupy much of the area of the chip, and in nanometer CMOS technology, interconnects dominate both performance and dynamic power dissipation, as signal propagation in wires across the chip requires multiple clock cycles

NoC is similar to a modern telecommunications network, using digital bit-packet switching over multiplexed links. An NoC is constructed from multiple point-to-point data links interconnected by switches (a.k.a. routers). NoC links can reduce the complexity of designing wires for

predictable speed, power, noise, reliability, etc

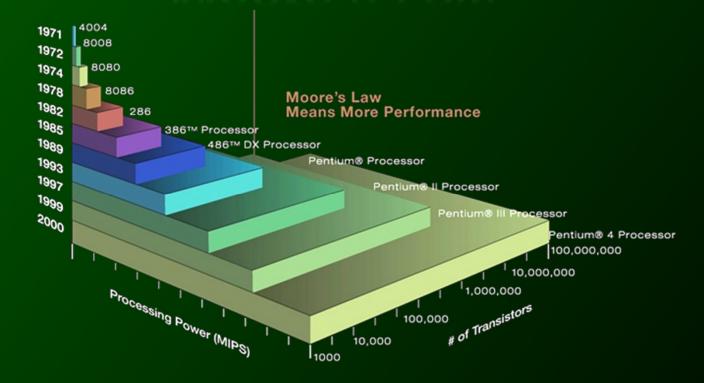

## Moore's Law

### Moore's Law, the empirical observation that the transistor density of integrated circuits doubles every 2 years.

Moore: Moore's law has been the name given to everything that changes exponentially. I say, if Gore invented the Internet, I invented the exponential.

## Moore's Law in Perspective

The number of transistors shipped in 2003 had reached about 10<sup>18</sup>. That's about 100 times the number of ants estimated to be in the world.

A chip-making tool levitated images within a tolerance of 1/10,000 the thickness of a human hair — a feat equivalent to driving a car straight for 1000 km while deviating less than one 3.8cm.

It would take you about 25,000 years to turn a light switch on and off 1.5 trillion times, but Intel has developed transistors that can switch on and off that many times each second..

## Moore's Law in Perspective

In 1978, a flight between New York and Paris cost around \$900 and took 7 hours. If the principles of Moore's Law had been applied to the airline industry the way they have to the semiconductor industry, that flight would now cost about a penny and take less than 1 sec.

The price of a transistor is now about the same as that of one printed newspaper character.

Intel has developed transistors so small that about 200 million of them could fit on the head of each of these pins.

## Intel µP Trends

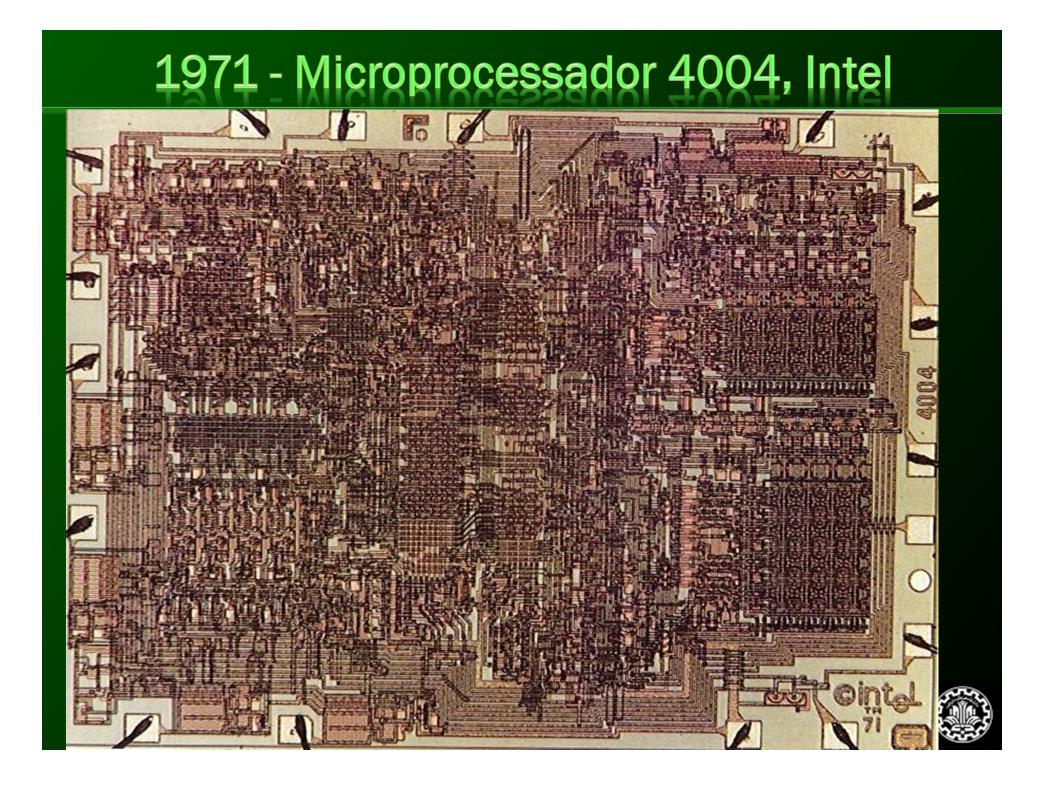

- Intel 4004: first single-chip microprocessor

- November 15, 1971

- Clock rate 740 kHz

- Bus Width 4 bits (multiplexed address/data due to limited pins)

- PMOS

- 2,300 Transistors at **10 µm**

- Addressable Memory 640 bytes

- Program Memory 4 KB (4 KB)

- Intel Core i7

- Today

- Clock rate 2.66GHz-3.33GHz

- 64 bit processor

- 4 cores

- 731M Transistors at **45 nm**

- Oregon 32 nm plant

- Price 273-562 \$

- 263 mm2 die size

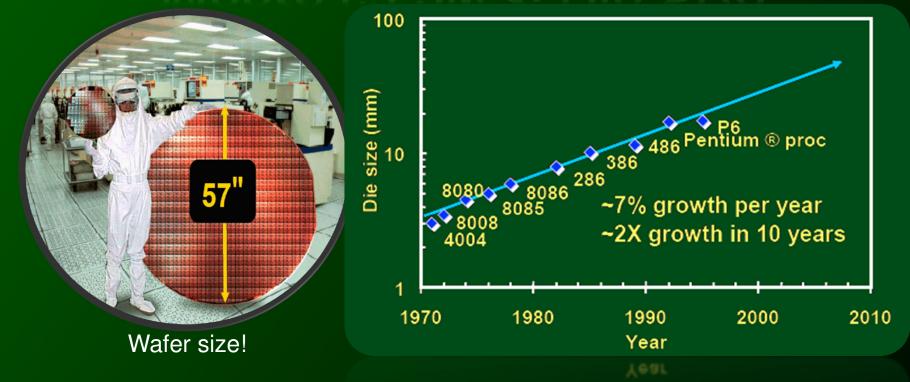

## Moore's Law & Die Size

Moore was not always accurate Projected Wafer in 2000, circa 1975 Die size has grown by 14% to satisfy Moor's law, BUT the growth is almost stopped because of manufacturing and cost issues

The die size of the processor refers to its physical surface area size on the wafer, the first generation Pentium used a 0.8 micron circuit size, and required 296 mm<sup>2</sup> per chip. The second generation chip had the circuit size reduced to 0.6 microns, and the die size dropped by a full 50% to 148 mm<sup>2</sup>!!!

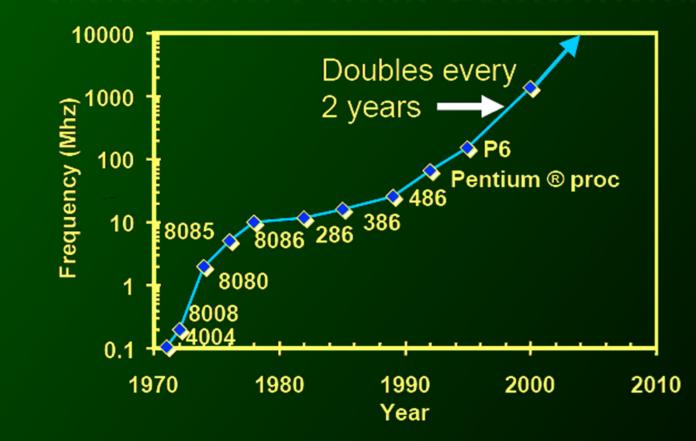

## **Trends in Clock Frequency**

Lead microprocessors frequency doubles every 2 year, BUT the growth is slower because of power dissipation issue

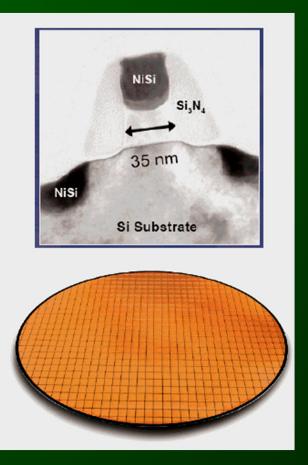

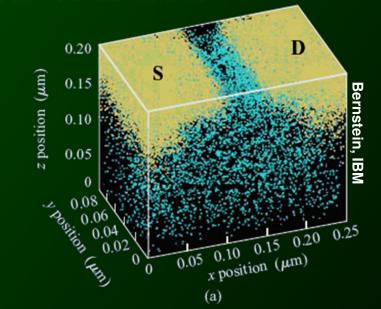

## MOS in 65nm

Distance between Si atoms = 5.43 °A

# of atoms in channel =

35 nm / 0.543 nm = 64 Atoms!

Problem: Uncertainty in transistor behavior and difficult to control variation! Randomly placed dopants in channel

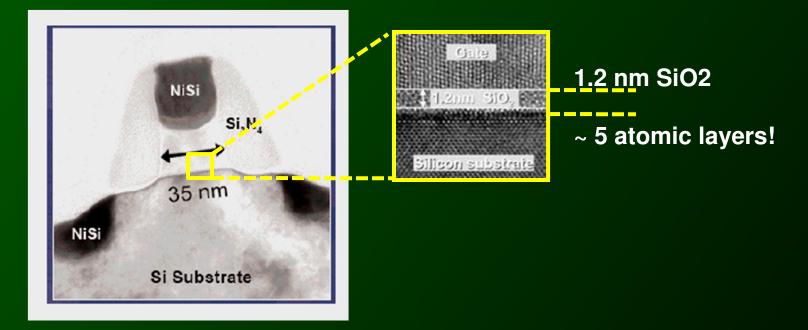

## Gate Insulator Thickness in 65nm

Problem: Electrons can easily jump over the 5 atomic layers! This is known as leakage current

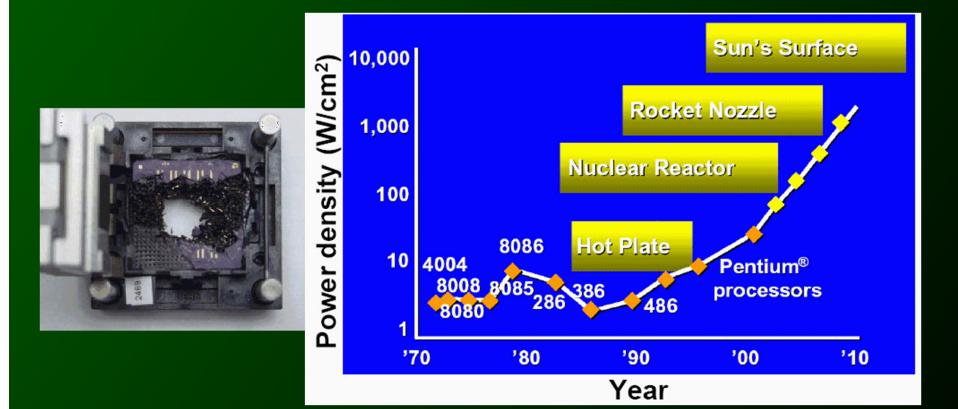

## **Power Density Problem**

Power density too high to keep junction at low temperature. Power reaching limits of air cooling.

## **Power Density Problem**

Power = 115 Watts Supply Voltage = 1.2 V Supply Current = 115 W / 1.2 V = 96 Amps!

Note: Fuses used for household appliances = 15 to 40 Amps

Problem: Current density becomes a serious problem! This is known as electromigration Power = 115 Watts Chip Area =  $2.2 \text{ cm}^2$ Heat Flux = 115 W /  $2.2 \text{ cm}^2$ =  $50 \text{ W/cm}^2$  !

Notes: Heat flux in iron =  $0.2 \text{ W/cm}^2$ Heat flux in frying pan =  $10 \text{ W/cm}^2$

Problem: Heat flux is another serious issue!

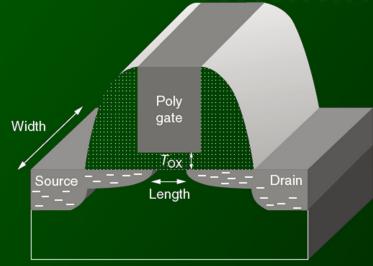

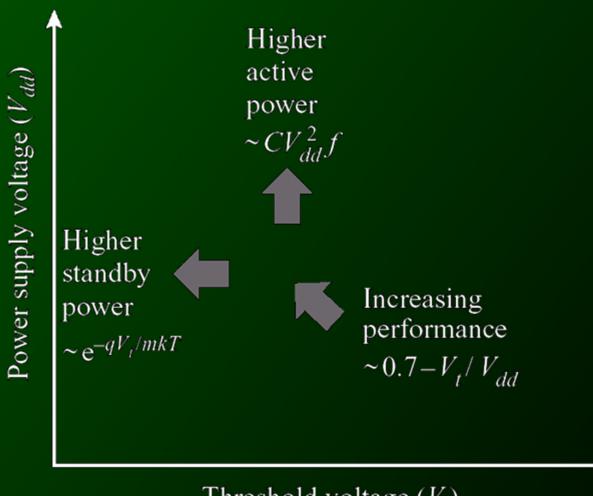

## **Transistor Scaling**

$$T_{Delay} = C_{Gate} \frac{V_{DD}}{I_{Drive}}$$

$$= \frac{WL}{T_{ox}} \frac{V_{DD}}{I_{Drive}}$$

$$I_{Drive} = \frac{W}{LT_{ox}} \cdot \left(V_{DD} - V_{Th}\right)^{2}$$

#### Scaling Issues:

- Channel length modulation

- Drain induced barrier lowering

- Punch through

- Sub-threshold current

- Field dependent mobility / Velocity saturation

- Avalanche breakdown and parasitic bipolar action

- Oxide Breakdown

- Interconnect capacitance

- Heat production

- Process variations

- Modeling challenges

$$T_{Delay} = L^2 \frac{V_{DD}}{\left(V_{DD} - V_{Th}\right)^2}$$

## Limit of "Moore's Law"?

- What is behind this fantastic race of development of the IC technologies?

- Is it the "technological" will and motivation of the people involved?

- Or/and is it the economical drive the main force?

- Semiconductor industry sales:

- **1962**, > \$1-billion

- **1978**, > \$10-billion

- **1994**, > \$100-billion

- 2 prominent technical: (DRAM), uP

- Will physics or economics stop Moore's law ?

### Physical limits to computation

The min. energy perform a logic operation in time  $\Delta t$

$E \ge \pi \hbar/2\Delta t$   $\hbar = 1.0545 \times 10^{-34} \text{ J.s}$

max # of operations per second  $N = 2E/\pi\hbar$

#

Entropy  $S = k_B \ln W$ # of states  $k_B = 1.3805 \times 10^{-23} \text{ J/K}$

of bits

$$m = S/k_B \ln 2$$

$$\frac{\text{operation}}{\text{bit.sec}} = \frac{N}{m} = \frac{2Ek_B \ln 2}{\pi \hbar S} \qquad \sim \frac{2k_B T \ln 2}{\pi \hbar}$$

minimal amount of energy required to 1 bit :  $\sim k_B T \ln 2$

38

#### Min. Transistor Switching Energy ITRS '97-'03 Gate Energy Trends 1.E-14 250 LP min gate energy, aJ 180 HP min gate energy, aJ 1.E-15 130 - 100 k(300 K) 90 In(2) k(300 K) 1.E-16 — 1 eV - k(300 K) 32 1.E-17 CVV/2 energy, 1.E-18 Room-temperature 100 kT reliability limit One electron volt 1.E-19 1.E-20 Room-temperature kT thermal energy Room-temperature von Neumann - Landauer limit 1.E-21 1.E-22 2005 2015 2025 2030 1995 2000 2010 2020 2035 2040 2045 Year 39

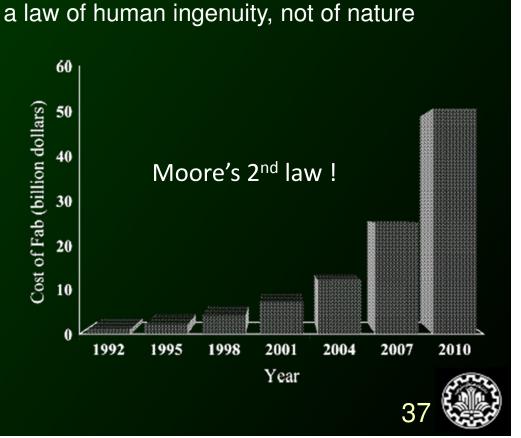

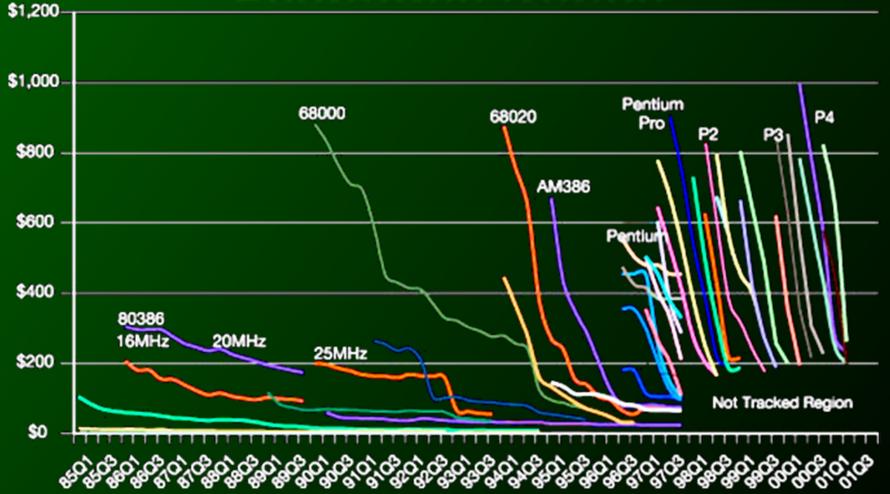

# Economic trends

Product lifecycles and the products selling prices are decreasing at an increasing rate. (Based on information from DataQuest and MicroDesign Resources)

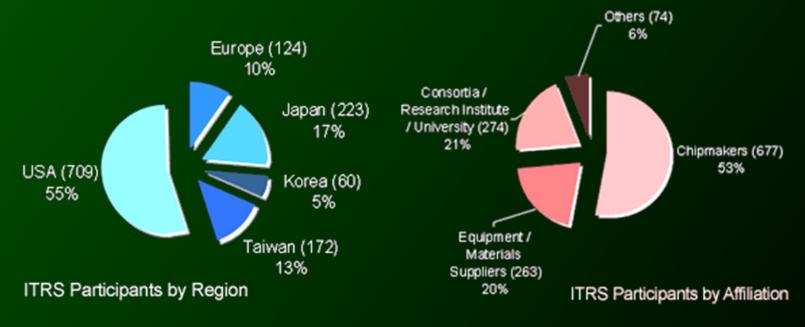

### ITRS

The International Technology Roadmap for Semiconductors is sponsored by the five leading chip manufacturing regions in the world: Europe, Japan, Korea, Taiwan, and the United States

http://www.itrs.net/reports.html

"Prediction is very difficult, especially if it's about the future" Niels Bohr

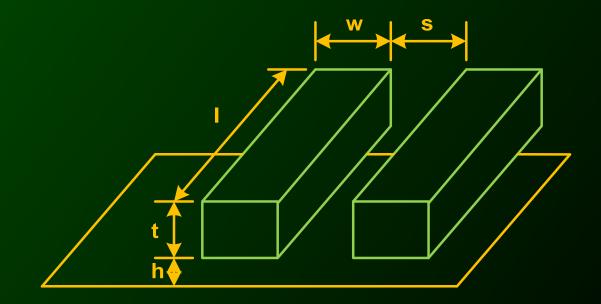

### Wire Geometry

○ Pitch = w + s

○ Aspect ratio: AR = t/w

○ Old processes had AR << 1</li>

Modern processes have AR ≈ 2

Pack in many skinny wires

# ITRS Interconnect Technology Requirement

#### Short Term

| Year of Production                                                                                                  | 2005     | 2006     | 2007     | 2008     | 2009     | 2010     | 2011     | 2012     | 2013     |

|---------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| DRAM ½ Pitch (nm) (contacted)                                                                                       | 80       | 70       | 65       | 57       | 50       | 45       | 40       | 36       | 32       |

| MPU/ASIC Metal 1 ½ Pitch<br>(nm)(contacted)                                                                         | 90       | 78       | 68       | 59       | 52       | 45       | 40       | 36       | 32       |

| MPU Physical Gate Length (nm)                                                                                       | 32       | 28       | 25       | 22       | 20       | 18       | 16       | 14       | 13       |

| Number of metal levels                                                                                              | 11       | 11       | 11       | 12       | 12       | 12       | 12       | 12       | 13       |

| Number of optional levels – ground planes/capacitors                                                                | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 4        |

| Total interconnect length (m/cm <sup>2</sup> ) –<br>Metal 1 and five intermediate<br>levels, active wiring only [1] | 1019     | 1212     | 1439     | 1712     | 2000     | 2222     | 2500     | 2857     | 3125     |

| FITs/m length/cm <sup>2</sup> × $10^{-3}$ excluding global levels [2]                                               | 4.9      | 4.1      | 3.5      | 2.9      | 2.5      | 2.3      | 2        | 1.8      | 1.6      |

| J <sub>max</sub> (A/cm <sup>2</sup> ) – intermediate wire<br>(at 105°C)                                             | 8.91E+05 | 1.37E+06 | 2.08E+06 | 3.08E+06 | 3.88E+06 | 5.15E+06 | 6.18E+06 | 6.46E+06 | 8.08E+06 |

| Metal 1 wiring pitch (nm)                                                                                           | 180      | 156      | 136      | 118      | 104      | 90       | 80       | 72       | 64       |

| Metal 1 A/R (for Cu)                                                                                                | 1.7      | 1.7      | 1.7      | 1.8      | 1.8      | 1.8      | 1.8      | 1.8      | 1.9      |

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

### **ITRS** Interconnect Technology Requirement

#### Long Term

| Year of Production                                                                                            | 2014     | 2015     | 2016     | 2017     | 2018     | 2019     | 2020     |

|---------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|

| DRAM ½ Pitch (nm) (contacted)                                                                                 | 28       | 25       | 22       | 20       | 18       | 16       | 14       |

| MPU/ASIC Metal 1 1/2 Pitch (nm)(contacted)                                                                    | 28       | 25       | 22       | 20       | 18       | 16       | 14       |

| MPU Physical Gate Length (nm)                                                                                 | 11       | 10       | 9        | 8        | 7        | б        | 6        |

| Number of metal levels                                                                                        | 13       | 13       | 13       | 14       | 14       | 14       | 14       |

| Number of optional levels – ground planes/capacitors                                                          | 4        | 4        | 4        | 4        | 4        | 4        | 4        |

| Total interconnect length (m/cm <sup>2</sup> ) – Metal 1 and five intermediate levels, active wiring only [1] | 3571     | 4000     | 4545     | 5000     | 5555     | 6250     | 7143     |

| FITs/m length/cm <sup>2</sup> × $10^{-3}$ excluding global levels [2]                                         | 1.4      | 1.3      | 1.1      | 1        | 0.9      | 0.8      | 0.7      |

| J <sub>max</sub> (A/cm <sup>2</sup> ) – intermediate wire (at 105°C)                                          | 1.06E+07 | 1.14E+07 | 1.47E+07 | 1.54E+07 | 1.80E+07 | 2.23E+07 | 2.74E+07 |

| Metal 1 wiring pitch (nm)                                                                                     | 56       | 50       | 44       | 40       | 36       | 32       | 28       |

| Metal 1 A/R (for Cu)                                                                                          | 1.9      | 1.9      | 2        | 2        | 2        | 2        | 2        |

Manufacturable solutions exist, and are being optimized Manufacturable solutions are known Interim solutions are known Manufacturable solutions are NOT known

### NTRS Roadmap

| Year<br>Parameter | 2003        | 2004        | 2005        | 2008        | 2011        | 2014        |

|-------------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Technology(nm)    | 120         | 110         | 100         | 70          | 50          | 35          |

| # of Transistors  | 95.2M       | 145M        | 190M        | 539M        | 1523M       | 4308M       |

| Clock Frequency   | 1724 MHz    | 1857 MHz    | 2000 MHz    | 2500 MHz    | 3000 MHz    | 3600 MHz    |

| Chip Area (mm²)   | 372         | 372         | 408         | 468         | 536         | 615         |

| Wiring Levels     | 8           | 8           | 8-9         | 9           | 9-10        | 10          |

| Pitch(L/I/G)(nm)  | 330/420/690 | 295/375/620 | 265/340/560 | 185/240/390 | 130/165/275 | 95/115/190  |

| A/R (L/I/G)       | 1.6/2.2/2.8 | 1.6/2.3/2.8 | 1.7/2.4/2.8 | 1.9/2.5/2.9 | 2.1/2.7/3.0 | 2.3/2.9/3.1 |

| Dielectric Const. | 2.2-2.7     | 2.2-2.7     | 1.6-2.2     | 1.5         | <1.5        | <1.5        |

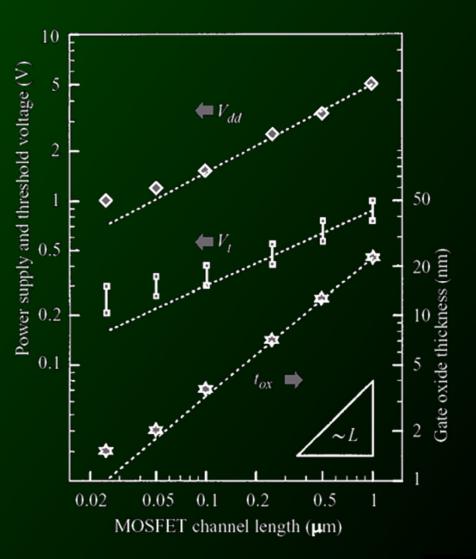

### **MOS Device Scaling**

Decreasing device sizes

reduce parasitic loads making

for faster transitions

$_{\odot}$  Increase variations between devices and across the die

Shrinking supply voltages increase noise sensitivity and reduce margins

System performance is limited by noise and clock skew

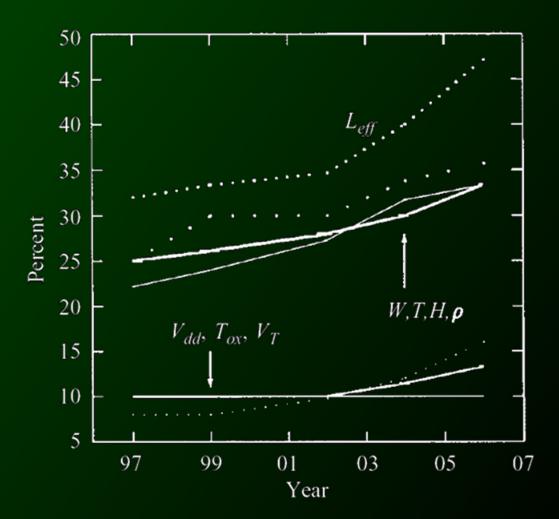

### **MOS Device Scaling**

Scaling induces increase

in magnitude of device to

device variations

Note particularly large increase in Leff => MOS current

### Vdd and Vt changes

Threshold voltage  $(V_t)$

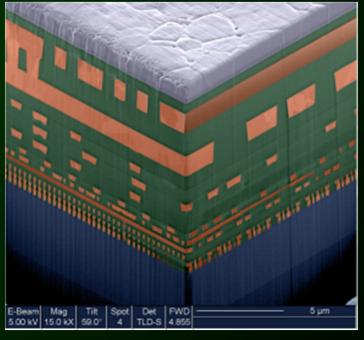

Metal stack over Silicon

- Reverse-scaled global interconnects:

- Growing interconnect complexity

- Performance critical global interconnects

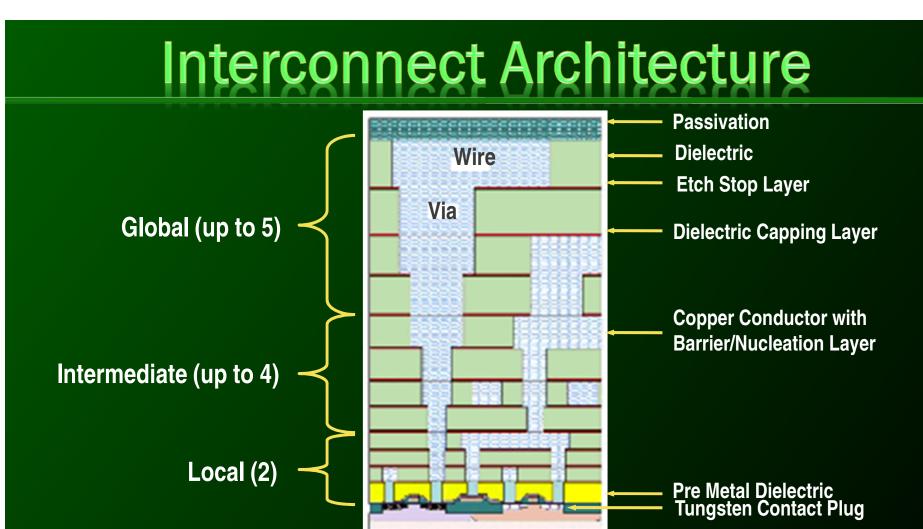

### Interconnect Architecture (Intel 130nm)

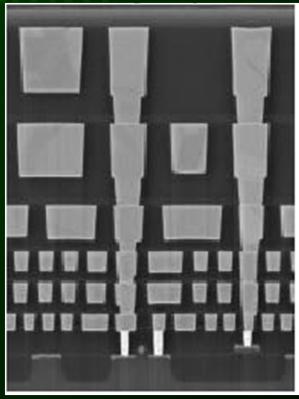

Intel 6LM 130nm process with vias shown (connecting layers)

| LAYER PITCH, THICKNESS AND ASPECT RATIO |            |            |              |  |  |  |

|-----------------------------------------|------------|------------|--------------|--|--|--|

| Layer                                   | Pitch (nm) | Thick (nm) | Aspect Ratio |  |  |  |

| Isolation                               | 3.64       | 450        |              |  |  |  |

| Poly-silicon                            | 336        | 160        |              |  |  |  |

| Metal I                                 | 350        | 280        | 1.6          |  |  |  |

| Metal 2, 3                              | 448        | 360        | 1.6          |  |  |  |

| Metal 4                                 | 756        | 570        | 1.5          |  |  |  |

| Metal 5                                 | 1120       | 900        | 1.6          |  |  |  |

| Metal 6                                 | 1204       | 1200       | 2.0          |  |  |  |

P. Bai et al, IEDM 2004

Real wiring cross section photograph

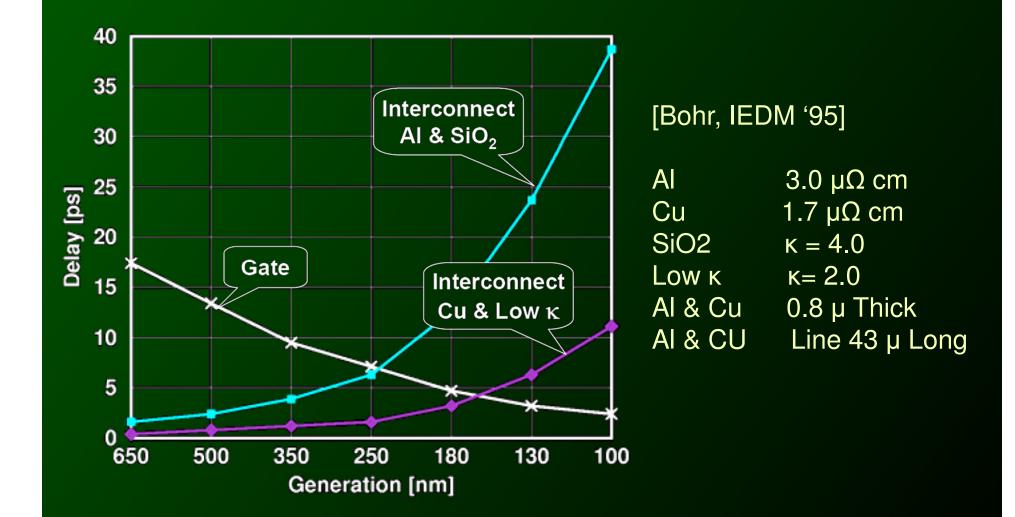

### Interconnect vs. Gate Delay

## **Choice of Metal**

- Until 180 nm generation, most wires were aluminum

- Modern processes often use copper Cu atoms diffuse into silicon and damage FETs Must be surrounded by a diffusion barrier

| Metal           | Bulk resistivity (mΩ*cm) |

|-----------------|--------------------------|

| Silver (Ag)     | 1.6                      |

| Copper (Cu)     | 1.7                      |

| Gold (Au)       | 2.2                      |

| Aluminum (Al)   | 2.8                      |

| Tungsten (W)    | 5.3                      |

| Molybdenum (Mo) | 5.3                      |

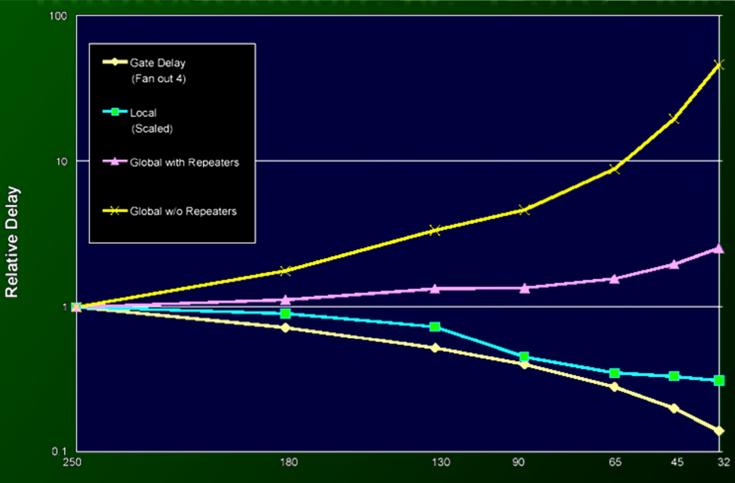

### Interconnects vs. Gate Delay

Process Technology Node (nm)

Delay for Metal 1 and global wiring vs feature size

### Interconnect Scaling Scenario

### Problem with Interconnects?

|                                                  | Technology generation |       |      |  |

|--------------------------------------------------|-----------------------|-------|------|--|

|                                                  | 1um                   | 100nm | 35nm |  |

| MOSFET switching delay (ps)                      | ~20                   | ~5    | ~2.5 |  |

| Interconnect <i>RC</i> response time, L=1mm (ps) | ~1                    | ~30   | ~250 |  |

| MOSFET switching energy (fJ)                     | ~30                   | ~2    | ~0.1 |  |

| Interconnect switching energy (fJ)               | ~40                   | ~10   | ~3   |  |

Calculations made by considering bulk resistivity of Cu

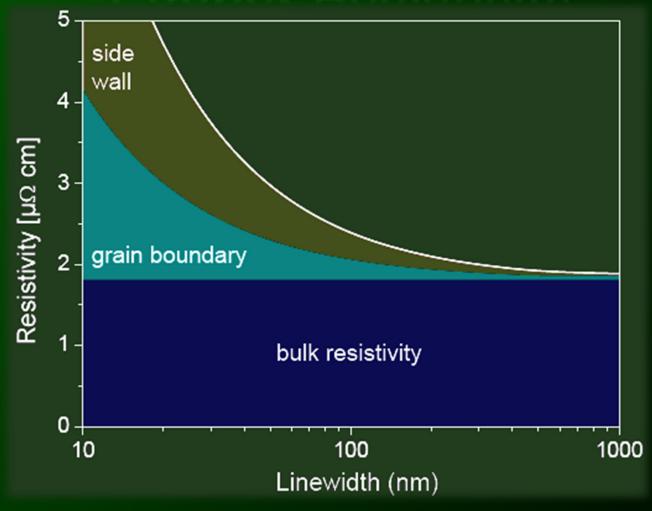

### **Copper Resistivity**

Resistivity of Cu increases with scaling

### Interconnect Resistance

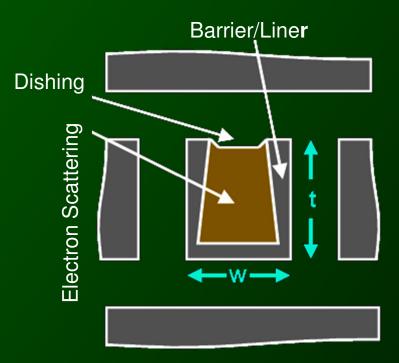

#### TiN

Barrier/Liner is usually another metal preventing Copper to diffuse into Si or SiO<sub>2</sub>

Diffusion barrier reduces wire's cross-section

Cu over polish (dishing) reduces it's thickness

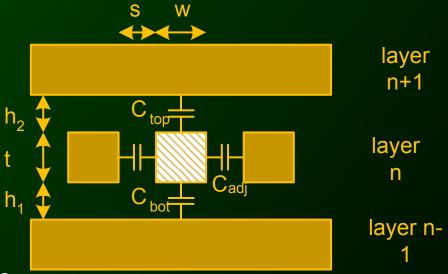

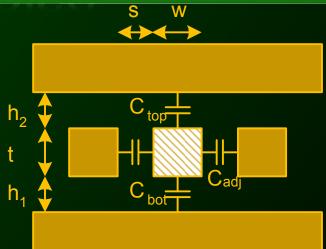

### Wire Capacitance

- Wire has capacitance per unit length To neighbors To layers above and below

C<sub>total</sub> = C<sub>top</sub> + C<sub>bot</sub> + 2C<sub>adi</sub>

- Parallel plate equation: C = eA/d

Wires are not parallel plates, but obey trends

Increasing area (W, t) increases capacitance

Increasing distance (s, h) decreases capacitance

plus a fringe term

- Dielectric constant

- $e = ke_0$

$$e_0 = 8.85 \times 10^{-14} \text{ F/cm}$$

$$k = 3.9$$

for SiO<sub>2</sub>

Processes are starting to use low-k dielectrics  $k \approx 3$  (or less) as dielectrics use air pockets

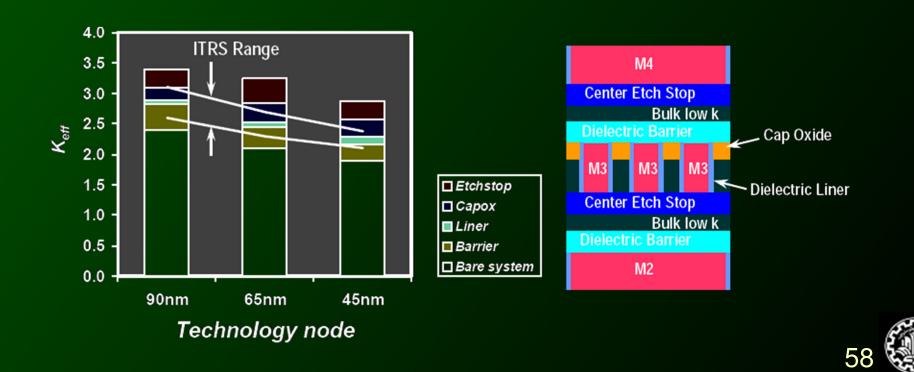

### **Capacitance** Extraction

$_{\odot}$  Extraction of interconnect capacitance in modern VLSI technology is complicated because of

Non-homogenous dielectric (etch stop, barrier liner, etc.)

Complex pattern of neighboring interconnects (need 3D modeling)

Sometimes, the overhead layers increases the effective K value

Overhead layers are hard to scale but needs to be controlled

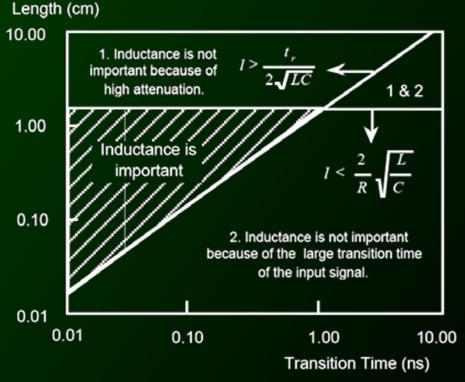

### Inductance Figure of Merit

Should we model wires as full transmission line? (no)

Unless we intentionally make inductance important: very wide wires

Or we are designing the clock grid

• Transmission line effects can be ignored if the wire is:

Very short, when signal transition is slower than the roundtrip delay

$t_r > 2L\sqrt{lc}$

Very long, when it becomes too lossy (resistance is more than 2Zo)

$rL > 2\sqrt{l/c}$

## **Problems of Inductance Modeling**

Extraction of on-chip inductance is very challenging

- Hard to define return path (unless we use partial inductance technique)

- Require a huge amount of netlist data (10x more than *RC* netlist data size)

- □ Simulation of on-chip inductance is also challenging

- Requires a lot more computation for delay calculation

- Available techniques have limited accuracy for large circuit structures

□ Fortunately, it is not required to include inductance for whole chip analysis

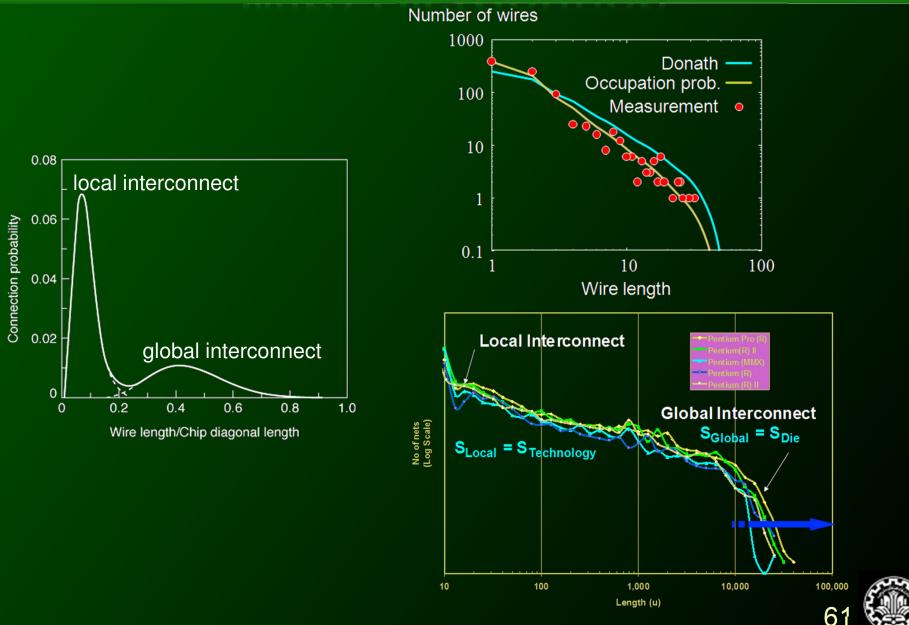

### Wire Distribution

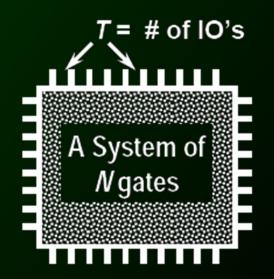

### **Rent's Rule**

Rent's Rule: Underlying assumption for system-level modeling

### $T = kN^p$

k and p are empirical constants such that:

k = average # of pins p = connectivity factor

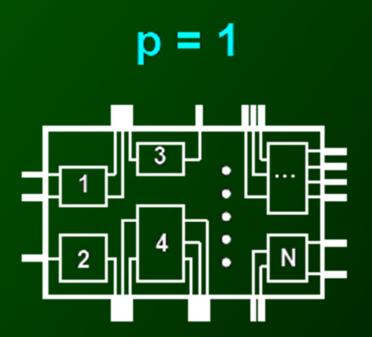

### **Rent's Rule**

No internal connection (T=kN)

Full internal connection (T=k)

p = 0

### **Delay Estimation Techniques**

#### □ SPICE Simulation

- Very slow not practical for chip level analysis

- Good for specific nets such as clocks or critical path

- Asymptotic Waveform Evaluation (AWE)

- Is an industry standard for delay estimation

• uses moment matching to determine a set of low frequency dominant poles that approximate the transient response

### Elmore Delay Analysis

- Uses only the first moment (dominant pole)

- Can be used for first order approximation in a complicated RC tree

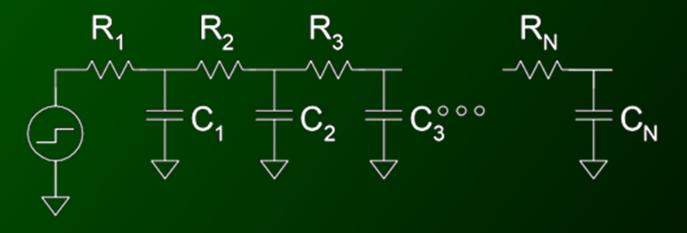

### Elmore Delay in RC Ladder

$$\tau_{Di} = \sum_{k=1}^{N} R_{ki} C_{k}$$

$$= P C + (P + P) C + (P + P) C$$

$= R_1 C_1 + (R_1 + R_2) C_2 + \dots + (R_1 + \dots + R_N) C_N$

## **Delay of Long Interconnect**

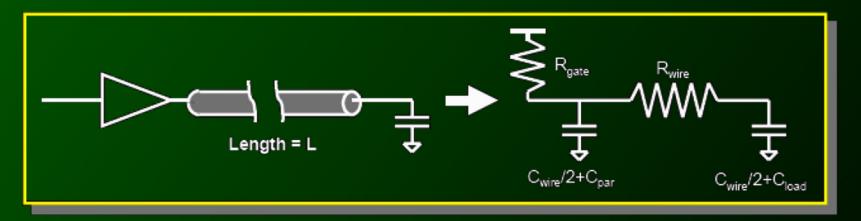

• Delay of gate driving a long wire governed by RC time constants

- Elmore delay:  $D = R_{gate}(C_{wire} + C_{par} + C_{load}) + R_{wire}(0.5C_{wire} + C_{load})$

Quadratic in total wire length

For long wires, this delay quickly becomes untenable In a 65nm process, wire delay looks like 2-3\*(gate delay)/mm2

### **Delay Reduction in Long Wires**

For slow long wires we use repeaters

Gain stages that break up the wire and "refresh" the signal Inverters are the simplest gain stage

Delay of a repeated line is linear in total length, not quadratic Delay is the geometric mean of the wire delay and the gate delay D = constant \* sqrt(gate\_delay \* RwCw)

### Noise: Power Supply

Resistive Voltage Drop and Simultaneous Switching Noise

Common Mode Supply Noise and Differential-Mode Supply Noise  $\Delta V_L = L(di/dt) \rightarrow$  Switching Noise (Dominant at Package Level)  $V = IR \rightarrow$  Very Dominant Noise for on chip power networks

Ground Bounce  $\rightarrow$  Ground noise

Power Bounce  $\rightarrow$  Noise Glitch on Power Line When Ground Bounce and Power Bounce are in Phase (Common Mode Noise) they will not effect the local logical cells but will degrade the signaling between distant Tx and Rx.

When Ground Bounce and Power Bounce are out of phase (Differential Mode Noise), they adversely effect the local logical cells causing jitter in timing circuits.

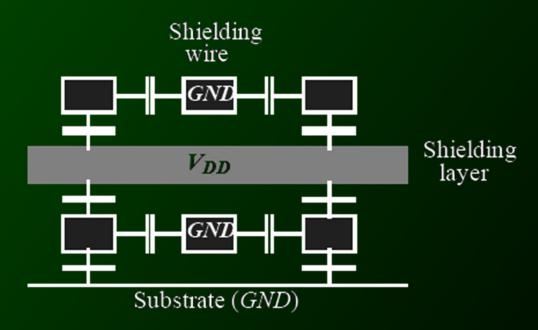

### Noise: Cross-Talk

Noise Caused by one signal, A, being coupled into another signal, B, is called Crosstalk.

Crosstalk may occur over many paths,

- a) Inductive Crosstalk and Capacitive crosstalk When the interconnects are routed close to each other, signals on the line crosstalk to each other via near field electromagnetic coupling.

- b) Substrate Crosstalk Common substrate will serve as a channel for signal coupling when Interconnects are placed far a apart. Such a noise source is called Substrate Crosstalk.

- c) Power/Ground Crosstalk

Signals can effect one another via a shared power supply and ground

Return Signal Crosstalk

When a pair of signals share a return path that has a finite impedance, a transition on one signal induces a voltage across the shared return impedance that appears as a noise on the other signal.

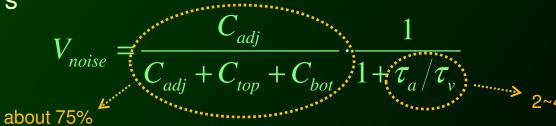

### Interconnect Noise

□ Wires are skinny and tall and have lots of sidewall capacitance

Aspect ratios at 2.2 now and are projected to scale up to 3-3.5 We will have to live with some coupled noise

$\Box$  Traditional estimates use a simple capacitive divider

$$V_{noise} = \frac{C_{adj}}{C_{adj} + C_{top} + C_{bot}}$$

But this is pessimistic, because the "victim" is usually driven, too

In reality, you must account for both victim and attacker drivers

To avoid cross talk noise

Prevent parallel lines

Shielding

7

### Electromigration

- Electromigration: Electrons smack into lattice, displacing atoms Caused by unidirectional current flow

Wires with bidirectional current is "selfhealing"

Copper's MTTF is 5x better than Aluminum's

- Highest at vias, where the current crowds from the vias

- □ Calculate max DC current, which depends on total capacitance Rule is "max current per wire cross section" (e.g., 1mA/µm<sup>2</sup>)

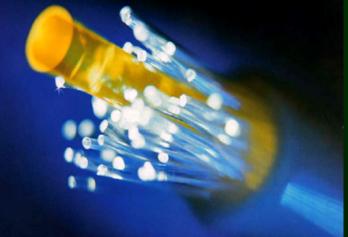

### **Replacing Wires?**

#### Papers on:

Interconnecting Chip Challenges \* Systems Interconnects \* High-Performance Computing \* Smart-Pixel Array Technology \* Plastic Micro-Optical Modules \* Embedded Guided Wave Interconnects \* Polymer Fiber Image Guides \* Chip/Board Challenges & Solutions \* FAST-Net Smart Prototype \* Parallel & Distributed Computing \* Neural & VLSI Architectures \* Scalable Parallel Computing Optical Fiber

Plus

Careers & Education Special: Skills for Engineering Entrepreneurs

Scanning Our Past from London: Crompton-A Different English Engineer!

#### **Optical interconnect**

BandwidthPowerDelay

## **Replacing Wire?**

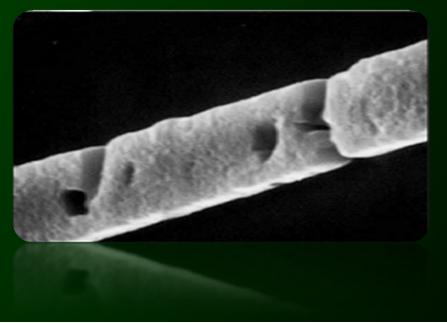

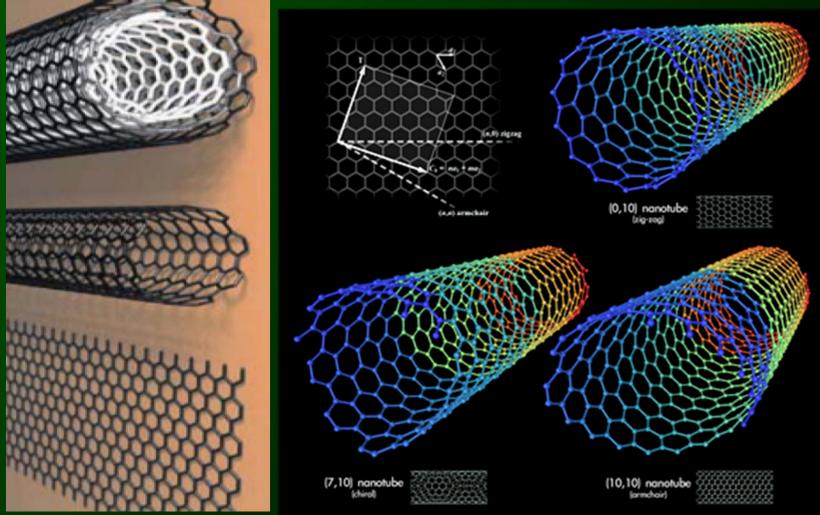

### $_{\odot}$ Sumio lijima of NEC in 1991

7

### **CNT** properties

Electrical:

• Ballistic conduction over distances of order 1 micron (~10<sup>-4</sup>  $\Omega$  cm).

- 'Metals' with low resistivity, Semiconductors with high mobility

- Conductivity a strong function of adsorbents or reactants.

Mechanical:

- High elastic modulus (high stiffness) (~1 to 5 TPa vs. ~0.2 for steel).

- Very high tensile strength (~10 to 100 GPa vs. ~1 for steel).

Thermal:

High room temperature thermal conductivity (~2000W/mK vs. ~400W/mK for copper).

Electrical Stability:

• Maximum current density ( 10<sup>9</sup> A/cm<sup>2</sup> vs. <10<sup>7</sup> A/cm<sup>2</sup> for Cu).

Chemical Stability:

C binding energy in graphene ~12 eV vs. Cu at a Cu surface ~ 4eV

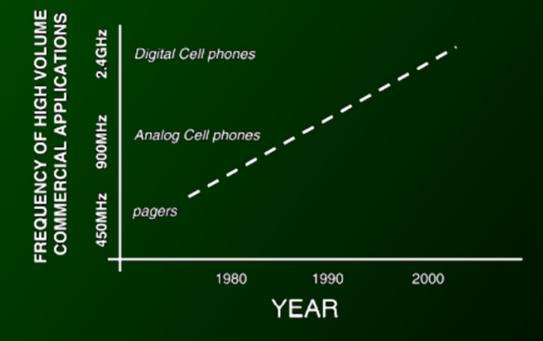

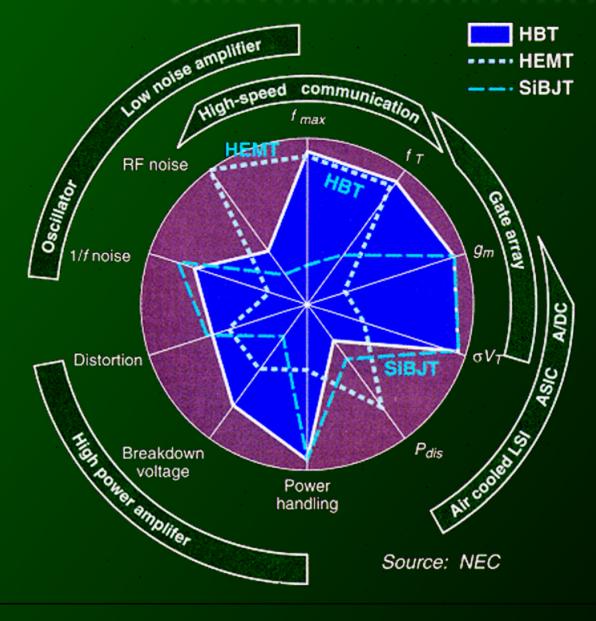

## SemiCond for Telecom.

rapid growth of the telecommunications  $\rightarrow$  compound semiconductors

- fiber-optic networks

- optoelectronic devices

- lasers

- detectors

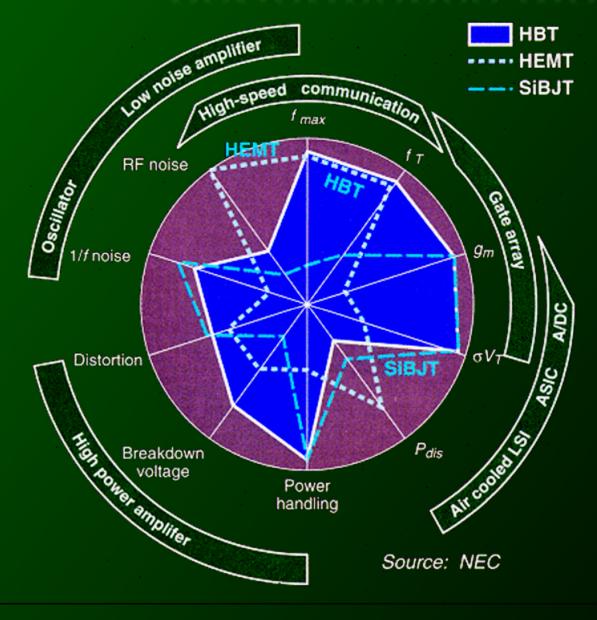

### performance metrics

Si BJT, HBT, and HEMT as a function of performance metrics

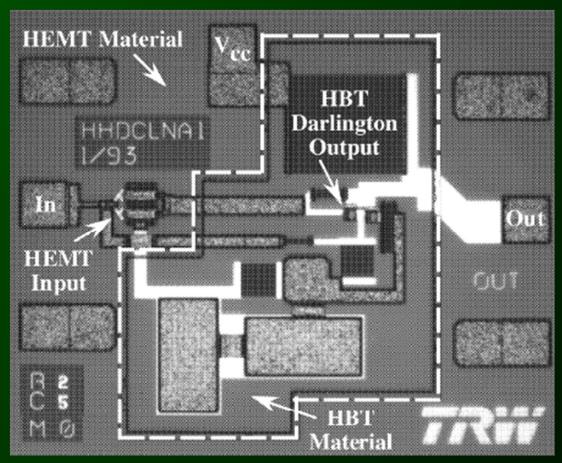

### Hetro - Integration

Integration of dissimilar device types: HEMTs and HBTs

### Silicon on Insulator

Advantages of SOI:

Reduced Source and Drain to Substrate Capacitance. Absence of Latchup Lower Passive current. Denser Layout  $\rightarrow$  Low cost Undopped Bulk!

#### SOI History!

1987: IBIS's commercial SIMOX (3"-6") wafer

1989: Tl's 64k SRAM

March 2004: Apple's Xserve G5 End 2004: AMD 90nm uP

# Silicon On Insulator Wafers (SOI)

Non-volatile:

ROM:

Mask ROM, PROM, EPROM, EEPROM

NVRAM:

Flash memory, ferroelectric RAM, Magnetoresistive RAM

Mechanical:

Magnetic tape, Hard drive, floppy disks, Optical drive

Volatile:

DRAM SRAM

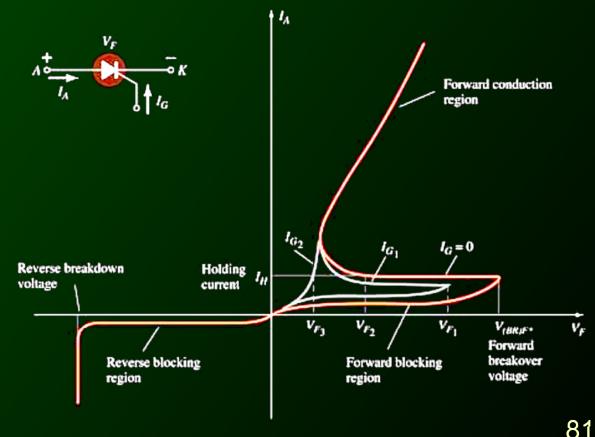

### pnpn devices

SCR—silicon silicon-controlled rectifier controlled rectifier SCS – silicon silicon-controlled switch controlled switch GTO – gate turn gate turn-off switch off switch LASCR – light-aActivated SCR Shockley diode Diac Triac

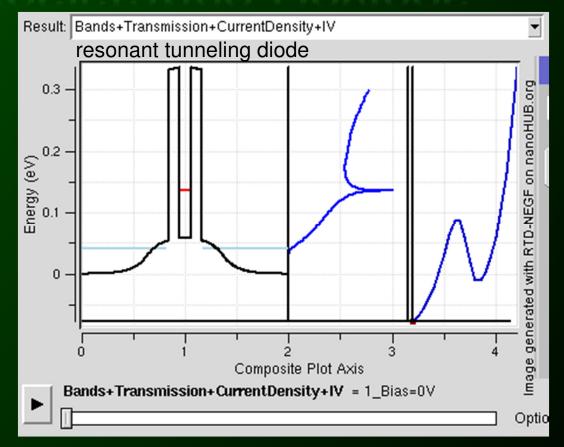

### **Negative Resistance Devices**

Negative Resistance Concept Tunnel Diodes IMPATT Diodes Gunn Effect Devices Power-Frequency Limitations BARITT and TRAPATT diodes

nature of optical transitions Recombination / Emission materials considerations internal and external quantum efficiencies modulation White Light Emitters Organic LEDs

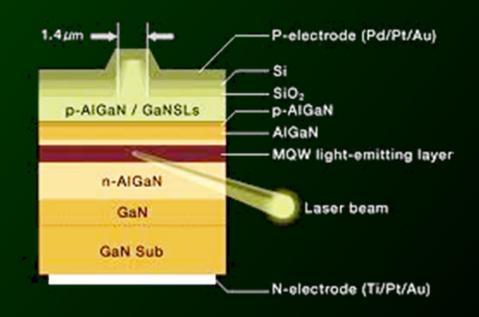

### Semiconductor lasers

- spontaneous and stimulated emission

- optical modes

- criterion for lasing

- heterostructures

- device structures and geometries

- single-frequency lasers and applications to fiber-optic communications

- modulation

- Side vs Vertical Emission

- Laser diode

### Photodetectors and solar cells:

- Light Absorption

- photoconductive and photovoltaic detectors

- noise considerations

- device structures and quantum efficiency

- avalanche photodiodes

- solar cell efficiency

- surface recombination effects

- tandem structures

- materials systems

- Avalanche Photodiodes

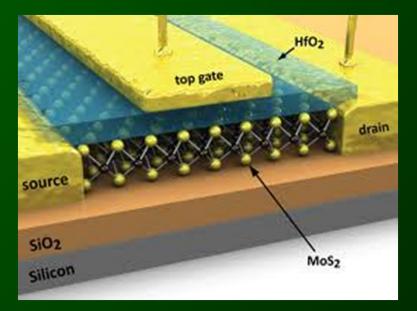

### Nanoelectronic Devices

### performance metrics

Si BJT, HBT, and HEMT as a function of performance metrics

### performance metrics